Hybrid Selective X-masking and X-canceling Multiple Input Signature Register for Test Data Compression Techniques

Xu Shubing

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Engineering in Computer Engineering

Prince of Songkla University

2011

**Copyright of Prince of Songkla University**

| Thesis Title   | Hybrid Selective X    | -masking and X-canceling Multiple Input Signature |

|----------------|-----------------------|---------------------------------------------------|

|                | Register for Test Dat | a Compression Techniques                          |

| Author         | Mr. Xu Shubing        |                                                   |

| Major Program  | Computer Engineerin   | ıg                                                |

| Major Advisor: |                       | Examining Committee:                              |

|                | weesak Reungpeerakul  | 1                                                 |

|                |                       |                                                   |

|                |                       | (Asst. Prof. Dr. Suntorn witosurapot)             |

|                |                       | (Asst. Prof. Dr. Chayanoot Sangwichien)           |

(Dr. Duenpen Kochakornjarupong)

.....

The Graduate School, Prince of Songkla University, has approved this thesis as partial fulfillment of the requirements for the Master of Engineering Degree in Computer Engineering.

.....

(Prof. Dr. Amornrat Phongdara)

Dean of Graduate School

| Thesis Title  | Hybrid Selective X-masking and X-canceling Multiple Input Signature |  |  |  |  |  |

|---------------|---------------------------------------------------------------------|--|--|--|--|--|

|               | Register for Test Data Compression Techniques                       |  |  |  |  |  |

| Author        | Mr. Xu Shubing                                                      |  |  |  |  |  |

| Major Program | Computer Engineering                                                |  |  |  |  |  |

| Academic Year | 2011                                                                |  |  |  |  |  |

## ABSTRACT

For test response compaction in Circuit-Under-Test (CUT) with scan-based Design-For-Test (DFT), the presence of Unknown-Values (X's) in test output responses during test can cause fault coverage lost and degrade the performance of test compression.

In this thesis, the present flexible X-masking logic called selective X-masking to handle the X's. The basic concept is to combine our X-masking logic with either X-canceling Multiple-Input-Signature-Register (MISR) or X-tolerant compactor. The selective X-masking is used to handle the majority of X's in scan chains, while the remained small number of X's can be tolerated by either X-canceling MISR or X-tolerant compactor. The experimental results based on ISCAS89 benchmark circuits have indicated that the presented selective X-masking logic can improve the compression ratio significantly and improve obviously the observability of scan cells.

Key words: X-masking, Test Response Compaction, MISR

# ACKNOWLEDGEMENT

The thesis, together with the 3 years study here is coming to an end. At this moment, I would like to extend my sincere thanks to all those who have concerned about or helped the writing.

My deepest gratitude goes first and foremost to Asst. Prof. Dr. Taweesak Reungpeerakul, he gives instructive advice and useful suggestions to me on my thesis. His understanding, patience, encouragements have been the most important factors which increase my confidence extremely.

Second, I would like to express my heartfelt gratitude to all lecturers in department of Computer Engineering, who helped me a lot on my study. Additionally, I would like to thank the graduate School, the staffs of Faculty of Engineering and the staffs of Department of Computer Engineering for giving the convenience for me.

Third, I would like to thank my friends for their supports and assistances.

Finally, my thanks would go to my beloved family for their loving considerations and great confidence in me all through these years.

Xu Shubing

# CONTENTS

| Page                                                | 3 |

|-----------------------------------------------------|---|

| CONTENTS                                            | 7 |

| LIST OF TABLES                                      | i |

| LIST OF FIGURES                                     | ζ |

| LIST OF ABBREVIATIONS AND SYMBOLSxi                 | i |

| CHAPTER                                             |   |

| I. INTRODUCTION                                     | Ĺ |

| 1.1 Motivation                                      | l |

| 1.2 Objective                                       | 3 |

| 1.3 Scope of Work                                   | ; |

| 1.4 Work Plan                                       | 3 |

| 1.5 Outline                                         | ł |

| 2. RESEARCH BACKGROUND                              | 5 |

| 2.1 Introductory Testing Concepts for VLSI Circuits | ; |

| 2.2 Introduction for Design for Testability (DFT)   | 3 |

| 2.2.1 Ad hoc DFT techniques                         | 3 |

| 2.2.2 Scan Design                                   | ) |

| 2.2.3 Built-In-Self-Test (BIST)                     | 3 |

| 2.3 Test Compression Techniques                     | 1 |

| 2.4 Test Stimulus Compression                       | 5 |

| 2.4.1 Code-Based Schemes                            | 5 |

| 2.4.2 Linear-Decompression-Based Schemes            | 1 |

| 2.4.3 Broadcast-Scan-Based Schemes                  | ) |

| 2.5 Test Response Compaction                        | l |

| 2.5.1 Space Compaction                              | 2 |

| 2.5.2 Time Compaction                               | 3 |

| 2.5.3 Finite Memory Compaction                      | ł |

| 2.6 Error Masking                                   | ; |

| 2.7 Summary                                         | 7 |

# **CONTENTS (CONTINUED)**

| Pag                                                          | ge |

|--------------------------------------------------------------|----|

| 3. RELATED SCHEMES FOR HANDLING UNKNOWN VALUES               | 28 |

| 3.1 Introduction of Schemes for Handling X's                 | 28 |

| 3.2 X-masking Techniques                                     | 29 |

| 3.2.1 Conventional LFSR X-masking                            | 29 |

| 3.2.2 Reiterative X-masking                                  | 31 |

| 3.2.2.1 Variable Reiterative X-masking                       | 31 |

| 3.2.2.2 Hybrid X-masking Approach                            | 33 |

| 3.2.3 Hierarchically Configurable Register                   | 35 |

| 3.2.3.1 Implement of Hierarchical Configurable Mask Register | 35 |

| 3.2.3.2 Optimal X-mask Determination                         | 37 |

| 3.3 X-tolerant Schemes                                       | 39 |

| 3.3.1 Response Reshape                                       | 39 |

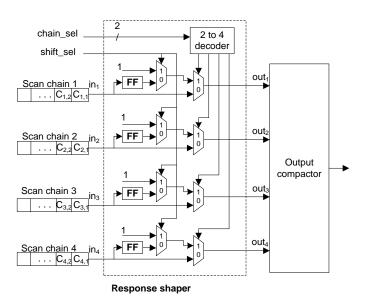

| 3.3.1.1Design of a Response Shaper                           | 40 |

| 3.3.1.2 Fault Detection with a Response Shaper4              | 12 |

| 3.3.1.3 Observable scan-out Response with a Response Shaper4 | 13 |

| 3.3.2 X-Canceling MISR4                                      | 14 |

| 3.3.2.1 Symbolic Simulation                                  | 14 |

| 3.3.2.2 X-Canceling MISR Architecture                        | 18 |

| 3.3.2.3 Combining X-masking and X-canceling MISR4            | 19 |

| 3.3.3 X-compactor                                            | 50 |

| 3.3.3.1 Compactor Design in the Absence of X's               | 50 |

| 3.3.3.2 Compactor Design in the Presence of X's              | 54 |

| 3.3.4 i-compactor                                            | 58 |

| 3.3.4.1 Design binary linear codes                           | 58 |

| 3.3.4.2 Examples                                             | 59 |

| 3.3.4.3 Handling More X's                                    | 50 |

| 3.4 Summary                                                  | 51 |

| 4. THE PROPOSED SELECTIVE X-MASKING AND RESULTS              | 53 |

| 4.1 Selective X-masking                                      | 53 |

# **CONTENTS (CONTINUED)**

|     | Page                                              |

|-----|---------------------------------------------------|

|     | 4.1.1The Process of Mask Bit Generation           |

|     | 4.1.2 Interval Counter                            |

|     | 4.1.3 Selection Register                          |

| 4.2 | An Example for Selective X-masking                |

| 4.3 | Combining with X-canceling MISR                   |

|     | 4.3.1 The Operation of the Hybrid Approach        |

| 4.4 | The X-tolerant Compactor with Selective X-masking |

| 4.5 | Results75                                         |

| 4.6 | Summary79                                         |

| 5.  | CONCLUSION AND DISCUSSION                         |

| 5.1 | Conclusion                                        |

| 5.2 | Discussion                                        |

|     | 5.2.1Advantages                                   |

|     | 5.2.2 Limitations                                 |

|     | 5.2.3 The future work                             |

| RE  | FERENCE                                           |

| AP  | PENDIX                                            |

|     | Published papers                                  |

| VI  | ۲ <b>AE</b> 98                                    |

# LIST OF TABLES

| Table                                                                         | Page |

|-------------------------------------------------------------------------------|------|

| 2.1 Typical Ad hoc DFT Techniques                                             | 9    |

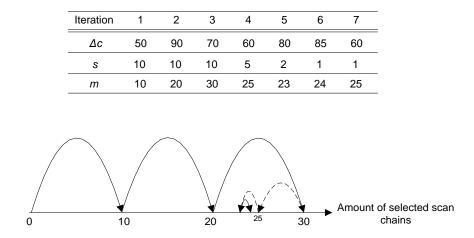

| 3.1 Example of iterative process                                              |      |

| 3.2 Error coverage versus Number of X-canceled combination (q)                | 47   |

| 3.3 Scan chains (without X) and compactor outputs                             | 53   |

| 3.4 Scan chains (with X) and compactor outputs                                | 56   |

| 3.5 The discussion for list schemes                                           | 62   |

| 4.1 ISCAS 89 benchmark circuit                                                | 76   |

| 4.2 Compression ratio with 0.5% X's                                           | 76   |

| 4.3 Comparison between with and without using selective X-masking with 1% X's | 77   |

| 4.4 Comparison between with and without using selective X-masking with 2% X's |      |

| 4.5 The overhead of mask bits based on 1% of X's                              | 78   |

| 4.6 The overhead of mask bits based on 2% of X's                              | 78   |

# LIST OF FIGURES

| Figure                                                           | Page |

|------------------------------------------------------------------|------|

| 2.1 Basic testing approach                                       | 5    |

| 2.2 VLSI development process                                     | 6    |

| 2.3 Design hierarchy                                             | 7    |

| 2.4 Observation point insertion                                  | 9    |

| 2.5 Control point insertion                                      | 10   |

| 2.6 Edge-triggered muxed-D scan cell design and operation        | 11   |

| 2.7 Clocked-scan cell design and operation                       | 12   |

| 2.8 Polarity-hold SRL design and operation                       | 13   |

| 2.9 Typical logic BIST system.                                   | 14   |

| 2.10 Block diagram illustrating test data bandwidth              | 15   |

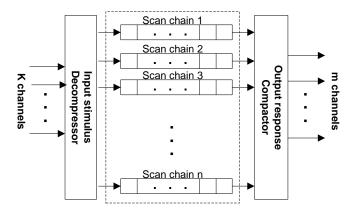

| 2.11 Architecture for test compression                           | 15   |

| 2.12 Test compression using a complete dictionary                | 17   |

| 2.13 Example of symbolic simulation for linear decompressor      | 18   |

| 2.15 Typical sequential linear decompressor                      | 20   |

| 2.16 Broadcasting to scan chains driving independent circuits    | 21   |

| 2.17 Compression scheme for scan-based designs                   | 22   |

| 2.18 Space compaction schemes for response data                  | 22   |

| 2.19 Basic space compactor structure                             |      |

| 2.20 Time compaction schemes for response data                   | 23   |

| 2.21 An <i>n</i> -stage multiple-input signature register (MISR) | 24   |

| 2.22 An equivalent <i>M</i> sequence for four-stage MISR         | 24   |

| 2.23 An example <i>q</i> -compactor with single output           | 25   |

| 2.24 Error masking in MISR                                       | 26   |

| 2.25 Error masking in space compactor                            |      |

| 3.1 A simple X-masking circuit                                   | 29   |

| 3.2 Architecture of conventional LFSR X-masking                  | 30   |

| 3.3 Conventional LFSR X-Masking Example                          | 30   |

| 3.4 Structure of variable reiterative LFSR X-Masking             | 31   |

| 3.5 Variable Reiterative LFSR X-Masking Example                  | 32   |

# LIST OF FIGURES (CONTINUED)

| Figure                                                                            | Page |

|-----------------------------------------------------------------------------------|------|

| 3.6 Hybrid X-Masking architecture                                                 | 33   |

| 3.7 Reiterative X-Masking Example                                                 | 34   |

| 3.8 Structure of hierarchical configurable mask register                          | 35   |

| 3.9 Mask register element for a single scan chain                                 | 36   |

| 3.10 4-stage mask register                                                        | 37   |

| 3.11 Development of the amount of masked scan chains during iterative process     |      |

| 3.12 Input compression and output compaction scheme with response shaper          | 40   |

| 3.13 An example of a 4-scan-chain response shaper                                 | 41   |

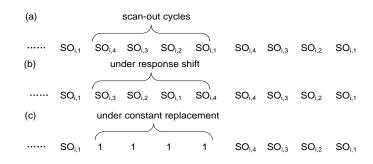

| 3.14 An example of shift operation and the replacement operation                  | 41   |

| 3.15 An example of fault detection with a response shaper                         | 42   |

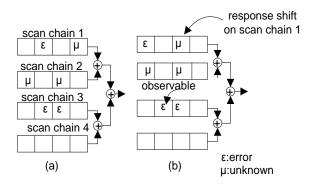

| 3.16 An example for observable scan-out response                                  | 43   |

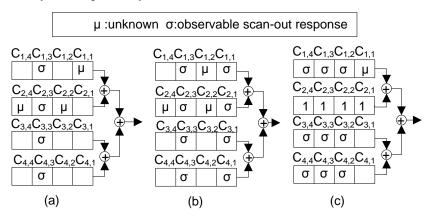

| 3.17 Example of Symbolic Simulation of MISR                                       | 45   |

| 3.18 Linear Equations for MISR in Figure 3.16                                     | 46   |

| 3.19 Gauss-Jordan Reduction of MISR Equations                                     | 47   |

| 3.20 X-Canceling MISR Architecture                                                | 48   |

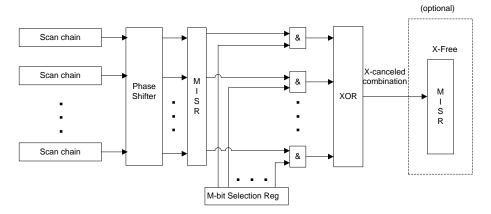

| 3.21 Combining X-masking and X-canceling MISR                                     | 49   |

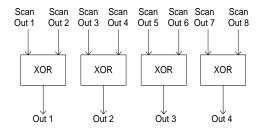

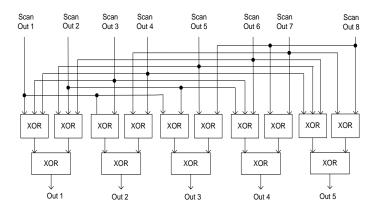

| 3.22 Compactor with eight inputs and outputs                                      | 51   |

| 3.23 Another compactor with eight inputs and four outputs                         | 51   |

| 3.24 X-compact matrices of Figure 3.21 and Figure 3.22                            | 52   |

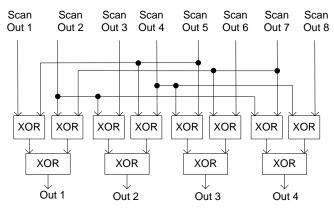

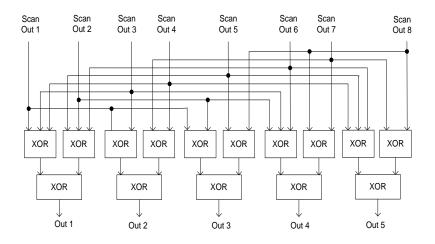

| 3.25 Compactor with eight inputs and five outputs with guaranteed error detection | 55   |

| 3.26 X-compact matrix for Figure 3.25 compactor                                   | 55   |

| 3.27 Submatrix of Figure 3.25                                                     | 56   |

| 3.28 The test system of i-compact                                                 | 58   |

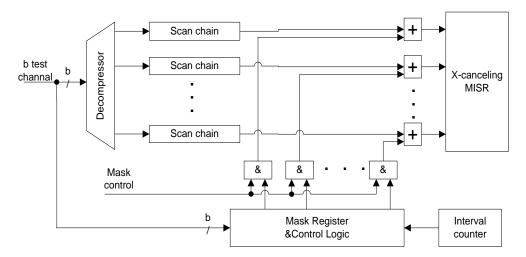

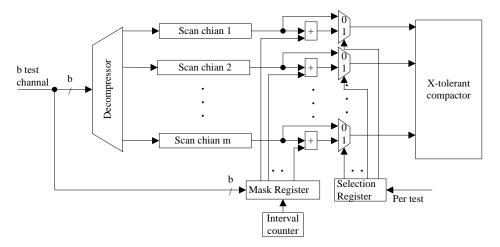

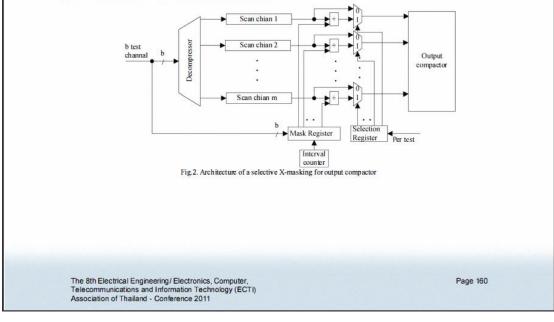

| 4.1 Architecture of selective X-masking for output compaction                     | 64   |

| 4.2 m-bit mask bit generation                                                     | 65   |

| 4.3 A 4-stage LFSR for mask bit generation                                        | 66   |

| 4.4 Create a mask for test responses (interval counter=3)                         | 67   |

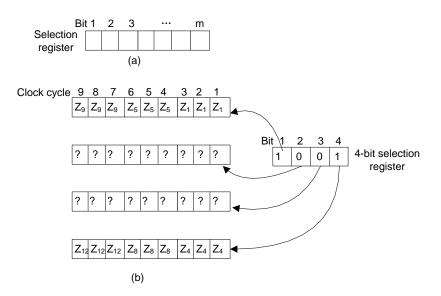

| 4.5 Create a mask for test response with selection register (interval counter=3)  | 67   |

| 4.6 An example for filling selection register and mask register                   | 69   |

# LIST OF FIGURES (CONTINUED)

| Figure                                                       | Page |

|--------------------------------------------------------------|------|

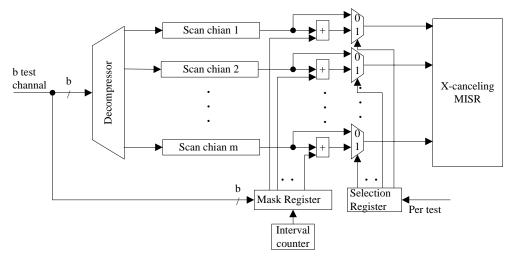

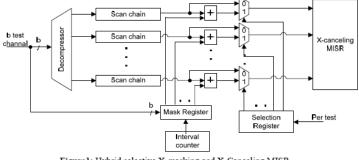

| 4.7 hybrid selective X-masking and X-canceling MISR          |      |

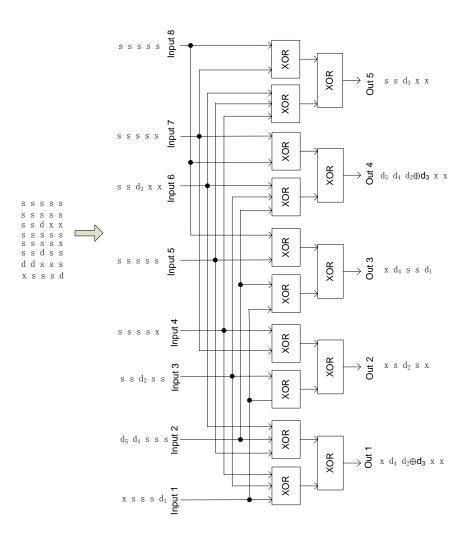

| 4.8 Output responses with eight scan chains                  | 70   |

| 4.9 An example for selective X-masking                       | 71   |

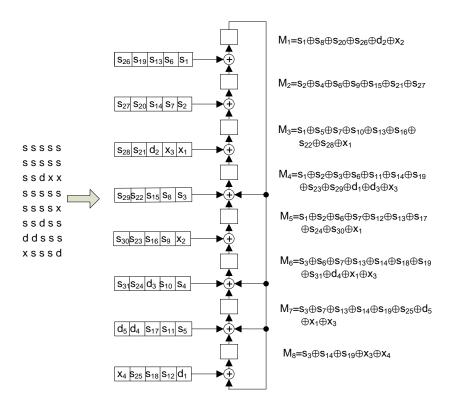

| 4.10 Example for symbolic simulation of MISR                 | 71   |

| 4.11 Linear equation for Figure 4.10                         | 72   |

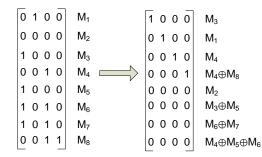

| 4.12 Gauss- Jordan elimination                               | 73   |

| 4.13 The X-tolerant compactor with selective X-masking logic | 73   |

| 4.14 Compactor with eight inputs and five outputs            | 74   |

| 4.15 X-compact matrix for Figure4.14 compactor               | 74   |

| 4.16 Example for compaction with X-compactor                 | 75   |

# LIST OF ABBREVIATIONS AND SYMBOLS

| DFT  | Design-for-Test                                                  |

|------|------------------------------------------------------------------|

| CUT  | Circuit-Under-Test                                               |

| ATE  | Automatic-Test -Equipment                                        |

| MISR | Multiple-Input -Signature -Register                              |

| SOC  | System-On-Chip                                                   |

| RTL  | Register-Transfer-Level                                          |

| CAD  | Computer-Aided -Design                                           |

| BIST | Built-In-Self-Test                                               |

| HCMR | Hierarchical-Configurable-Mask-Register                          |

| LFSR | Linear-Feedback-Shift-Register                                   |

| VLSI | Very-Large-Scale-Integration                                     |

| IC   | Integrated-Circuit                                               |

| РСВ  | Printed-Circuit-Board                                            |

| VHDL | Very-High-Speed-Integrated-Circuit-Hardware-Description-Language |

| MUX  | Multiplexer                                                      |

| TM   | Test-Mode                                                        |

| SE   | Scan-Enable                                                      |

| DI   | Data-Input                                                       |

| SI   | Scan-Input                                                       |

| DCK  | Data-Clock                                                       |

| SCK  | Shift-Clock                                                      |

| SRL  | Shift-Register-Latch                                             |

| LSSD | Level-Sensitive-Scan-Design                                      |

| TPG  | Test-Pattern-Generator                                           |

| ORA  | Output-Response-Analyzer                                         |

| X's  | Unknown-Values                                                   |

| ATPG | Automatic-Test-Pattern-Generation                                |

| CR   | Configuration-Register                                           |

| MR   | Mask-Register                                                    |

# LIST OF ABBREVIATIONS AND SYMBOLS (CONTINUED)

- OP Observation-Point

- CK Clock

- CP Control-Point

# **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Motivation

The scan based test is one of the best approaches [1-3] in DFT which is used to increase the circuit's controllability and observability. The objective is to improve the testability of a design and to reach the target fault coverage goal. The scan test allows the test data coming from CUT to be stored on the Automatic-Test-Equipment (ATE) in a compressed form. The test data stored in ATE for stimulus compression and output response compaction determines the total test data overhead, and the test application time depends on the length of scan chains [4]. In order to reduce test cost in industry design, the initial long scan chains are also cut into large number of shorter scan chains. As the increasing huge test data volume in industry design, researches have recently being focused on input stimulus compression and output response compaction in order to reduce the number of test channels on the ATE, tester memory and test time.

The response compaction is implemented and received data from the outputs of the scan chains. The main purpose of the response compaction is to reduce the amount of test response transferred back to the ATE. A large number of test response compaction schemes have been proposed. Basically they include the space compaction [5] and the time compaction [6]. It is possible to combine time and space compaction, such as finite memory compactor [7] [8] which give advantage of time and space dimensions.

For the output response compaction, the presence of X's in the test responses has been the greatest barrier to effect the compaction. If there are no X's in the test responses, a time compactor, such as MISR, can compact an infinitely long output sequence into a fixed-length signature [9]. However, when X's appear in the test responses, it can cause an unpredictable signature, from which no faulty-circuit signature could be distinguished. When X's are introduced to the space compactors, the non-X test responses in the current clock cycle going through the compactor are XORed by X's, then the non-X values are corrupted and the fault coverage might be lost. One of the major issues for test compaction is how to handle test responses containing X's. The sources of X's are caused by several conditions such as bus contention, uninitiated memory, un-modeled logic, floating tri-states bus, etc.

Lots of schemes have been proposed to handle X's in the output response. The widely used techniques to handle X's are X-blocking [10], X-masking [11-14] and X-tolerant [15-17]. The X-blocking scheme needs extra logic in the CUT [15], which can cause fault coverage lost and additional area overhead. Several X-masking techniques were proposed in previous work [11-13]. In one of X-masking techniques, the conventional Linear-Feedback-Shift-Register (LFSR) X-masking scheme [13] guarantees to mask all X's and keeps specified bits (d's) as well, where each value contained by d's is used to detect one or more faults. However, a large amount of mask data was generated for masking every scan slice. Another X-masking scheme is called reiterative X-masking [14], the volume of mask data decreases greatly due to reusing the mask bit. It is necessary to use interval counter for controlling.

Instead of masking X's, X-tolerant schemes have been introduced in [15] [17]. In [15], XOR gates are used to minimize the impact of non-X value being masked by X's. Since it can guarantee to check erroneous compactor output in the presence of limited number of X's, the errors can be detected by the tester when the errors are propagated to the compactor outputs with X's appearing in the current cycle. In the schemes of [17], there are N scan chains and the compacted test responses outputs are M, where N>M. In order to detect faults, the test responses from scan chains containing d's and X's are propagated to the different compactor outputs. However, the compaction ratio is extremely degraded as the increasing X's and the corrupted outputs by X's may decrease the fault coverage.

In this research, an efficient approach is developed based on the X-masking technique .It can reduce a large amount of mask bits without losing fault coverage in the presence of X's in test responses. The following main contents will be described from chapter 2 through chapter 5: the research background of compaction techniques and impact of X's in the test responses; the literature review on handling X's by focusing on several types of X-masking and

X-tolerant techniques; the proposed method; conclusion and discussion, respectively.

### 1.2 Objective

- 1) To reduce masking data overhead for test responses.

- 2) To improve the observability for scan cells in the presence of X's.

- To improve the efficiency of X-masking when the distribution of X's has the tendency to be clustered in the output responses.

### 1.3 Scope of Work

- Study the scan design in DFT method for Very-Large-Scale-Integration (VLSI) and the test architecture for test compression.

- Study test response compaction focusing on X-masking and X-tolerant techniques.

- 3) Implement and analyze X-masking scheme.

## 1.4 Work Plan

- To investigate and research on the basic idea of X-masking and X-tolerant schemes.

- 2) To find out an efficient X-masking technique for reducing the mask bits

- **3**) To present the proposal.

- 4) To implement the reiterative X-masking scheme and compute the total overhead of mask bits based on the ISCAS89 benchmark circuits.

- 5) To compare the performance between the proposed scheme and previous appproaches.

- To combine the selective X-masking for measuring the observability of scan cells.

- 7) To analyze implementation results and make a conclusion.

- 8) To submit the proposed papers in the international conferences and write the

final report.

# 1.5 Outline

This document is organized in 5 chapters as follow:

Chapter 1: Introduction. The motivation, objective and the scope of thesis are presented in this chapter. Then, the work plan for investigating the X-masking schemes is given as follow.

Chapter 2: Research Background. It includes the DFT architecture, scan test compression techniques and the problem statement in the presence of X's.

Chapter 3: Related schemes for handling unknown values. In this chapter, the wildly used schemes are described to handle X's in the output responses including X-masking and X-tolerant schemes. It discusses the issues about achieving high fault coverage and high compression ratio in the presence of X's.

Chapter 4: The proposed Selective X-masking and Results. A flexible X-masking logic is introduced in this section. The basic operation and principle based on the distribution of X's are presented.

Chapter 5: Conclusion and discussion.

# **CHAPTER 2**

## **RESEARCH BACKGROUND**

### 2.1 Introductory Testing Concepts for VLSI Circuits

Testing techniques for VLSI circuits are now facing many excited and complex challenges. As the continuously shrinking technologies in the large systems embedded in a single System-On-Chip (SOC), the right behavior of the whole systems is very important. The electronic testing consists of Integrated-Circuit (IC) testing, Printed-Circuit-Board (PCB) testing, and system testing at the various manufacturing stages during the whole system operation. The main function of testing is not only to find the fault-free systems but also to improve production yield at the various stages of manufacturing by analyzing the cause of defects when faults are encountered. In some systems, the periodic testing is implemented to ensure fault-free system operation and to initiate repair procedures once the faults are detected. Hence the VLSI testing techniques is very important for all the designers, product engineers, test engineers, manufacturers, and end-users [18].

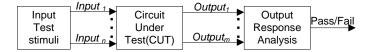

Testing typically includes the parts of applying a set of test stimuli to the inputs of CUT and analyzing the output responses, as showed in Figure 2.1.Circuits that produce the correct output responses for all input stimuli are considered to be fault-free. The circuits that produce an incorrect response at any point during simulation are assumed to be faulty. Testing is performed in different stages in the lifecycle of VLSI device, such as during the VLSI development process, the electronic system manufacturing process, and, in some cases, system-level operation.

Figure 2.1 Basic testing approach [9]

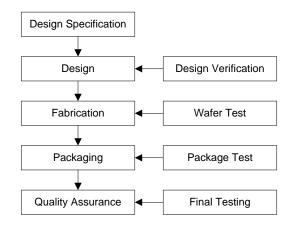

For the VLSI development process, it can be seen that some form of testing is involved at each stage of the process in Figure 2.2. The VLSI device that fulfills the customer or project requirement is determined and formulated as a design specification. Design verification is a predictive analysis to ensure that the synthesized design can perform the function requirement when it is manufactured. Designers are responsible for synthesizing a circuit that satisfies the design specification and for verifying the design. Once a design error is found, the design is necessary to be modified and design verification must be repeated. As a result, design verification can be considered as a form of testing.

Figure 2.2 VLSI development process [9]

After that, then the VLSI design comes to fabrication. It is necessary to develop a test procedure based on the design specification and fault models at the same time. Since it is impossible for 100% of any particular kind of IC to be defect-free due to unavoidable statistical flaws in the materials, the ICs fabricated test on the wafer is the first test during the manufacturing process in order to determine which devices are defective. After passing the wafer-level test the chips are extracted and packaged. The packaged devices need to be retested because those devices may have been damaged during the packaging process or put into defective packages. The last test is the final testing before the chips go to market, including measurement of such parameters as input/output timing specifications, voltage, and current. In addition, stress or burn-in testing is often performed where chips are subjected to high temperatures and supply voltage. In a word, the design verification is very important for the VLSI development process and

even for the whole VLSI testing.

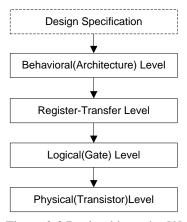

For the design specification, it can be divided into several levels, as shown in Figure 2.3. The design process is always transformed from a higher level description to lower level description. The initial level is a behavioral level which is developed in Very-High –Speed-Integrated-Circuit-Hardware-Description-Language (VHDL) or Verilog or as a C program and simulated to determine if it is functionally equivalent to the specification. After that, the design comes to Register-Transfer-Level (RTL) level description, which is verified with the functionality of the behavioral level and performed with more structural information including the data paths and control circuits. The logic level is synthesized from the RTL description and is designed to guarantee the correct functionality. For the physical level description, the physical placement is obtained and the transistors in the VLSI device are interconnected to fabrication.

Figure 2.3 Design hierarchy [9]

Many tools have been developed for design verification process such as Computer-Aided-Design (CAD), synthesis, hardware emulation, and formal verification methods. However, design verification takes time, and insufficient verification fails to detect design errors. Thus, the process of the design verification is extremely important. Moreover, the test stimuli are often applied to design verification of the RTL, logical, and physical levels for testing the VLSI device.

Normally, the following two undesirable situations may occur after ICs are

tested:

1. A faulty device appears to be a good part passing the test.

2. A good device fails the test and appears as faulty.

These two situations happen often due to a poorly designed test or the lack of DFT. For the first case, even if all products pass acceptance test, some faulty devices can be found in the manufactured electronic system. The next section will give the basic background for DFT.

#### 2.2 Introduction for DFT

A substantial amount of time and effort is required when test engineers usually have to construct test vectors after the design is completed. However, the effort can be avoided if testing is considered early in the design flow to make the design more testable. Hence, integration of design and test, referred to as DFT, was first proposed in the 1970s. In order to test circuits, we need to control and observe logic values of internal lines. However, it would be very difficult to control and observe some nodes in sequential circuits. Testability measures of controllability and observability were first defined in the 1970s, which is considered to find some parts of a digital circuit that will be most difficult to test in test pattern generation for fault detection. Many DFT techniques have been proposed since that time as generally falling into three categories: (1) Ad hoc DFT techniques, (2) Scan design (3) Built-In-Self-Test (BIST).

### 2.2.1 Ad hoc DFT techniques

Ad hoc methods were the first DFT techniques proposed in the 1970s [1]. It targets only those portions of the circuit that would be difficult to test. Ad hoc DFT techniques typically involve applying good design practices or replacing a bad design practice with a good one. Table 2.1 lists some typical ad hoc techniques. One of the most widely used techniques is test point insertion. The conception is to insert test point directly to access internal nodes to improve the controllability or observability.

Table 2.1 Typical Ad hoc DFT Techniques

| A1 | Insert test points                                |

|----|---------------------------------------------------|

| A2 | Avoid asynchronous set/reset for storage elements |

| A3 | Avoid combinational feedback loops                |

| A4 | Avoid redundant logic                             |

| A5 | Avoid asynchronous logic                          |

| A6 | Partition a large circuit into small blocks       |

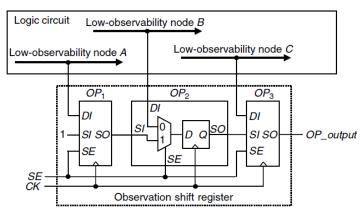

The observation point insertion for a logic circuit with three low-observability nodes is shown in Figure 2.4. Observation-Point (OP) shows the structure of an observation point that consists of a Multiplexer (MUX) and a D flip-flop. It includes the Scan –input (SI) and Scan-Output (SO). A low-observability node is connected to the port '0' of the MUX for an observation point, and all observation points are serially connected into an observation shift register using the port '1' of the MUX. An Scan-Enable (SE) signal is applied to select MUX port. The multiplexer uses SE input to select between the Data-Input (DI) and the Scan-Input (SI) .When *SE* is set to 0 and the Clock (CK) is applied, the logic values of the low-observability nodes are captured into the D flip-flops. When *SE* is set to 1, the D flip-flops within OP1, OP2, and OP3 operate as a shift register, allowing us to observe the captured logic values through OP\_output during sequential clock cycles. As a result, the observability of the circuit nodes is greatly improved.

Figure 2.4 Observation point insertion [9]

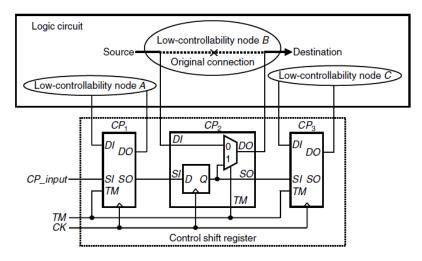

Figure 2.5 shows an example of control point insertion for a logic circuit with three low-controllability nodes. The Control-Point (CP) is composed of a MUX and a D flip-flop. It includes the basic SI and SO. The original connection at a low-controllability node is cut, where a MUX is inserted between the source and destination ends. During normal operation, the Test-Mode (TM) is set to 0 and the CK is applied, the value drives from the source end to the destination end through the port'0' of the MUX. During test model, TM is set to 1 so that the value from the D flip-flop drives the destination end through the port'1' of the MUX. The D flip-flops in OP1, OP2, and OP3 are designed to form a shift register so the required values can be shifted into the flip-flops using CP\_input. Hence, the controllability of the circuit nodes is greatly improved. However, the control point insertion can result in additional delay to the logic path. So the control points can't be inserted on a critical path.

Figure 2.5 Control point insertion [9]

### 2.2.2 Scan Design

There are basically two input sources in a scan cell. The first input, data input, is driven by the combinational logic of a circuit. The second input, scan input, is driven by the output of another scan cell in order to form one or more shift registers called scan chains. The scan chain is performed by connecting the scan input of the first scan cell to a primary input and the output of the last scan cell to a primary output. In order to allow a scan cell to operate in two different modes: normal/capture mode and shift mode, a selection mechanism must be provided.

In normal/capture mode, data input is selected to update the output. In shift mode, scan input is selected to update the output.

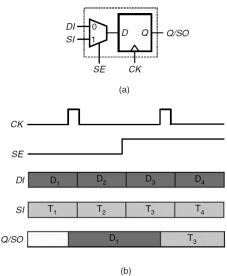

The Muxed-D scan design is one of the most widely used schemes in logic design. The basic operation is o pass a logic value from its input to its output when a clock is applied. The muxed-D scan cell design is shown in Figure 2.6(a). It consists of a D flip-flop and a multiplexer. The multiplexer uses SE input to select between the Data-Input (DI) and the Scan-Input (SI). During normal/capture mode, *SE* is set to 0, and the value in the input DI is captured into the internal D flip-flop when a rising clock edge is applied. In shift mode, SE is set to 1. The SI is now used to shift in new data to the D flip-flop while the content of the D flip-flop is being shifted out. Sample operation waveforms are shown in Figure 2.6(b).

Figure 2.6 Edge-triggered muxed-D scan cell design and operation [9]

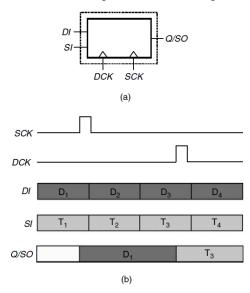

A clock-scan cell design was another important approach proposed in [2]. Comparing with a muxed-D scan cell, a clocked-scan cell also has a data input DI and a scan input SI; however, the input selection in the clocked-scan cell is applied with two independent clocks, Data-Clock (DCK) and Shift-Clock (SCK), as shown in Figure 2.7(a). In normal/capture mode, the present value at the data input DI is captured into the clocked-scan cell by data clock DCK. During shift mode, the shift clock SCK is used to shift in new data from the scan input SI into the clocked-scan cell, while the current content of the clocked-scan cell is being shifted out. Sample operation waveforms are shown in Figure 2.7(b). The main advantage is that it can result in no performance degradation on the data input. However, it requires additional shift clock routing.

Figure 2.7 Clocked-scan cell design and operation [9]

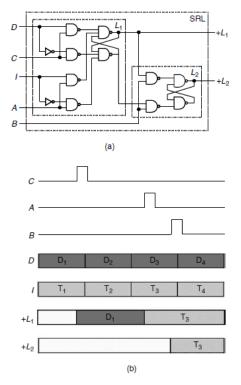

Different from muxed-D scan cells or clocked-scan cells using for edge triggered, flip-flop-based designs, the Level-Sensitive-Scan-Design (LSSD) scan cell is used for level-sensitive, latch-based designs [19] [20] [21]. Figure 2.8(a) shows a polarity-hold Shift-Register-Latch (SRL) design described in [19] that can be used as an LSSD scan cell. This scan cell consists of two latches, a master two-port D latch L<sub>1</sub> and a slave D latch L<sub>2</sub>. Clocks C, A, and B are used to select between the data input D and the scan input I to drive  $+L_1$  and  $+L_2$ , which can be used to drive the combinational logic of the design. In capture mode, master latch L1 uses the system clock C to latch system data from the data input D and to output this data onto  $+L_1$ . In shift mode, clocks A and B are used to latch scan data from the scan input I and to output this data onto  $+L_2$ . Sample operation waveforms are shown in Figure 2.8(b).

The main advantage of LSSD is to insert scan into a latch-based design. But the technique requires routing for the additional clocks, which increases routing complexity.

Figure 2.8 Polarity-hold SRL design and operation [9]

## 2.2.3 Built-In-Self-Test (BIST)

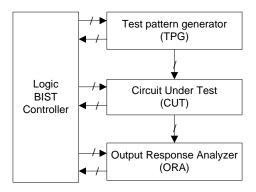

BIST was proposed around 1980 [3] [22], which integrate a Test-Pattern-Generator (TPG) and an Output-Response-Analyzer (ORA) in the VLSI device to perform testing internal to the IC, as illustrated in Figure 2.9. The test pattern can be generated automatically by TPG for application to the inputs of the CUT. The ORA is then applied to compact the output responses of the CUT into a signature. The logic BIST controller can generate specific BIST timing control signal for coordinating the BIST operation among the TPG, CUT, and ORA. During the BIST operation, the compacted final signature needs to compare with an embedded golden and the logic BIST controller then provides a pass/fail indication. The compaction for output responses requires that all storage elements in the TPG, CUT, and ORA must be initialized to known state, which means that no X could be propagates from the CUT to the ORA.

Figure 2.9 Typical logic BIST system [9]

Scan DFT techniques have been wildly used in the industry. Some of major elements for scan test cost are: (1) test data volume, which translates to tester memory requirement; (2) total number of tester channels;(3) test time, which translates to the maximum number of flip flops in a scan chain. As the IC chip complexity increases, test data volume also increases rapidly. Since test data volume is a major factor that determines test cost, several test compression techniques to reduce both volume of test patterns and output responses have been developed, which is described in next.

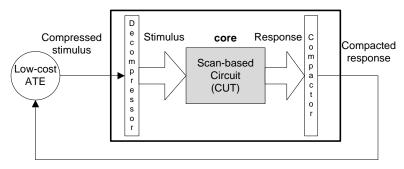

### 2.3 Test Compression Techniques

For the test compression, it involves the amount of compressing data including both stimulus and response that is stored on ATE for testing with a deterministic test set. The benefit of test compression is that the amount of test data can achieve a  $10 \times$  or even  $100 \times$  reduction on the ATE. The ATE memory requirements are greatly reduced and even more importantly it reduces test time because less data has to be transferred across the bandwidth between the ATE and the chip. Moreover, the test compression techniques are easy to implement in industry design because they are compatible with the conventional design rules and test generation flows used for scan testing.

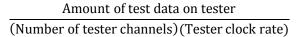

Figure 2.10 shows the test data bandwidth between the tester and the chip. As

ATE has limited speed, memory, and I/O channels, the chip cannot be tested any faster than the amount of time required to transfer the test data, and the time is equal to:

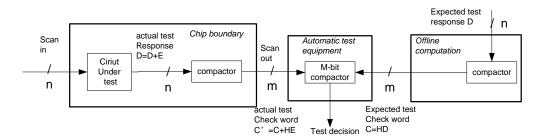

Figure 2.10 Block diagram illustrating test data bandwidth [9]

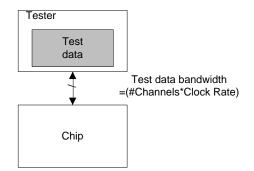

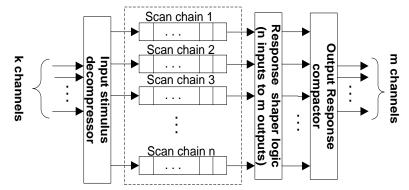

Test compression technique is to compress the test data stored on ATE including both stimulus and responses, and the structure is illustrated in Figure 2.11. It can largely reduce the total amount of tester memory. Moreover, the test time can be obviously reduced due to less test data transferred across the low bandwidth link between the tester and the chip. It shows that the additional on-chip hardware is integrated before the scan chains to decompress the test stimulus coming from the tester and after the scan chains to compact the response going to the tester.

Figure 2.11 Architecture for test compression [9]

## 2.4 Test Stimulus Compression

Test data is inherently highly compressible. In fact, typically only 1 to 5% of the bits have specified values, and majority of unspecified bits that are not assigned values during Automatic-Test-Pattern-Generation (ATPG). Consequently, test stimulus compression can be used to significantly reduce the amount of test stimulus data that must be stored on the tester. Normally, ATPG procedures perform random fill, in which all the unspecified bits in the test cubes are filled randomly with 1's and 0's to create fully specified test vectors. During test stimulus compression procedure, the specified (care) bits should be lossless in order to preserve the fault coverage of the original test cubes. After decompression, the resulting test patterns shifted into the scan chains should match the original test cubes in all the specified bits. Many compressing schemes have been proposed, which can be classified into the three categories: (1) Code-based techniques, (2) Linear-decompression-based schemes (3) Broadcast-scan-based schemes.

#### 2.4.1 Code-Based Schemes

In order to encode the test cubes, the data compression codes partition the original data into symbols which can be replaced with a codeword to form the compressed data. The decompression is performed by using a decoder that simply converts each codeword into the corresponding symbol. Depending on whether the size of symbols and codewords is fixed or variable, data compression codes can be classified into four categories.

Take a dictionary code (fixed-to-fixed) for example, which had been proposed in [23]. There are n-bits blocks to form the symbols in the original test cubes, and then the symbols are encoded with codewords that each has b bits, where b<n. One can view each symbol through dictionary because each codeword has been indexed into the dictionary that points to the corresponding symbol. Since there are 2n possible for symbols and 2b possible for codewords, no all possible symbols can be in the dictionary. If S<sub>data</sub> is the set of symbols that occur in the original data, the number of distinct symbols that occur in the original data  $|S_{data}|$  is much less than 2<sup>n</sup>. The compression ratio is equal to:

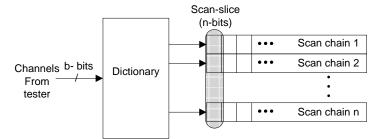

The scheme is shown in Figure 2.12. There are n (n>=1) scan chains, and the test cubes are partitioned into n-bit symbols such that each scan slice corresponds to a symbol. The size of each codeword is b bits, where  $b = \lceil \log_2 |s_{data} | \rceil$ . This figure shows that the b channels from the tester can be used to load n scan chains. Normally, b channels can just load b scan chains from the tester. Thus, the length of each scan chain becomes shorter and less clock cycles are required. The dictionary code gives a good example for how test compression reduces not only tester storage but also test time.

Figure 2.12 Test compression using a complete dictionary [9]

#### 2.4.2 Linear-Decompression-Based Schemes

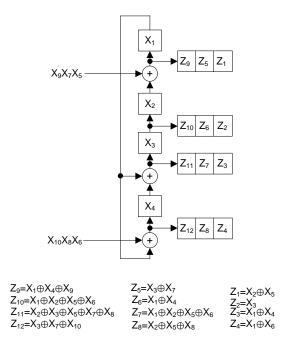

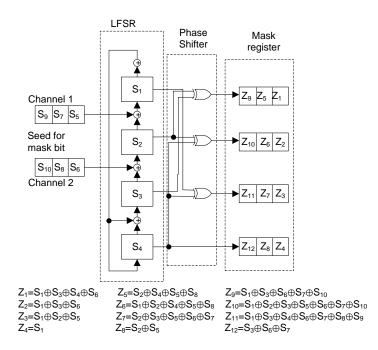

Another test stimulus compression scheme is to expand the original data from the tester to scan chains by using linear decompressor, which consists of only XOR gates and flip-flops. The linear space can be spanned by a Boolean matrix. In other words, the linear decompressor can expand an m-bit compressed stimulus from the tester into an n-bit test vector, the set of test vectors that can be generated by the linear decompressor is spanned by A, and a Boolean matrix is  $A_{n\times m}$ . Any test vector Z can be compressed by a particular linear decompressor if and only if there exists a solution to a system of linear equations, AX = Z, where A is the characteristic matrix of the linear decompressor and X is a set of free variables stored on the tester. There is an example of a sequential linear decompressor shown in Figure 2.13, where each free variable coming from the tester is represented by a symbol. The initial state of the LFSR is represented by the free variables  $X_1-X_4$ , and the free variables  $X_5-X_{10}$  are shifted in by two channels as the scan chains are loaded. After symbolic simulation, the characteristic matrix for a linear decompressor can be obtained and the final values in the scan chains are represented by the equations for  $Z_1$ - $Z_{12}$ .

Figure 2.13 Example of symbolic simulation for linear decompressor [9]

The operation of symbolic simulation is shown as follow: Assume that the initial seed  $X_1-X_4$  have been already loaded into LFSR. In the first cycle, the top flip-flop is filled by the XOR of  $X_2$  and  $X_5$ , the second flip-flop is filled by  $X_3$ , the third flip-flop is filled by the XOR of X1 and X4, and the bottom flip-flop is filled by the XOR of X1 and X4, and the bottom flip-flop is filled by the XOR of X1 and X6. Finally, it gets  $Z_1=X_2\oplus X_5$ ,  $Z_2=X_3$ ,  $Z_3=X_1\oplus X_4$ , and  $Z_4=X_1\oplus X_6$ .

In the second cycle, the top flip-flop is filled by the XOR of  $X_3$  and  $X_7$ , where  $X_3$  is the contents of the second flip-flop; the second flip-flop is filled by the values of the third flip-flop  $(X_1 \oplus X_4)$ ; the third flip-flop is filled by the XOR of the values of the first flip-flop  $(X_2 \oplus X_5)$  and the fourth flip-flop  $(X_1 \oplus X_6)$ ; and the bottom flip-flop is filled by the XOR of the values of the first flip-flop  $(X_2 \oplus X_5)$  and  $X_8$ . Thus, it can get  $Z_5 = X_3 \oplus X_7$ ,  $Z_6 = X_1 \oplus X_4$ ,  $Z_7 =$  $X_1 \oplus X_2 \oplus X_5 \oplus X_6$ , and  $Z_8 = X_2 \oplus X_5 \oplus X_8$ . In the third cycle, the top flip-flop is filled by the XOR of the values of the second flip-flop  $(X_1 \oplus X_4)$  and  $X_9$ ; the second flip-flop is filled by the values of the third flip-flop  $(X_1 \oplus X_2 \oplus X_5 \oplus X_6)$ ; the third flip flop is filled by the XOR of the values of the third flip-flop  $(X_1 \oplus X_2 \oplus X_5 \oplus X_6)$ ; the third flip flop is filled by the values of the first flip-flop  $(X_3 \oplus X_7)$  and the fourth flip-flop  $(X_2 \oplus X_5 \oplus X_8)$ ; and the bottom flip-flop is filled by the XOR of the values of the first flip-flop  $(X_3 \oplus X_7)$  and  $X_{10}$ . Thus, it gets  $Z_{9} = X_4 \oplus X_9$ ,  $Z_{10} = X_1 \oplus X_6$ ,  $Z_{11} = X_2 \oplus X_5 \oplus X_8$ , and  $Z_{12} = X_3 \oplus X_7 \oplus X_{10}$ . At the moment, the scan chains are fully loaded with a test cube and the whole simulation is complete. The corresponding system of linear equations for this linear decompressor is shown in Figure 2.14.

|   |          |   |   |   |   |   |   |   |   |                |                    | 77                                           |

|---|----------|---|---|---|---|---|---|---|---|----------------|--------------------|----------------------------------------------|

| 1 | <b>0</b> | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | <b>0</b> 1     |                    | $\begin{bmatrix} \mathbf{Z}_1 \end{bmatrix}$ |

|   | 0        | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0              | [ X <sub>1</sub> ] | Z <sub>2</sub>                               |

|   | 1        | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | Ō              | X <sub>2</sub>     | Z <sub>3</sub>                               |

|   | 1        | ŏ | ŏ | Ō | Ŏ | 1 | Ŏ | ŏ | Ŏ | ŏ              | X <sub>3</sub>     | Z <sub>4</sub>                               |

|   | 0        | Õ | 1 | Õ | Õ | 0 | 1 | 0 | Ŭ | Ő              | X <sub>4</sub>     | $ \mathbf{Z}_{5} $                           |

|   |          | 0 | 0 | 1 | 0 | 0 | 0 | 0 |   | o              | $X_5$              | $ \mathbf{Z}_6 $                             |

|   | 1        | U | U | T | U | U | U | U | 0 | νı             | <b>**</b> 5        |                                              |

|   | 1        | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0              | X <sub>6</sub>     | - Z <sub>7</sub>                             |

|   | 0        | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0              | X <sub>7</sub>     | Z <sub>8</sub>                               |

|   | 1        | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0              | X <sub>8</sub>     |                                              |

|   | 1        | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0              | X <sub>9</sub>     | Z <sub>10</sub>                              |

|   | 0        | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0              | X <sub>10</sub>    |                                              |

|   | L0       | Δ | 1 | Δ | Δ | 0 | 1 | 0 | Δ | 1              | -10-               | <u>[</u> <u></u> 11]                         |

| 1 | -0       | U | 1 | 0 | 0 | U | 1 | U | 0 | 1 <sup>」</sup> |                    | $\lfloor \mathbf{Z}_{12} \rfloor$            |

Figure 2.14 System of linear equations for the decompressor [9]

For the linear decompressor, the linear equations can be used to encode the test cube and can be solved with the Gauss–Jordan elimination [24]. The test cube that does not find a solution is called unencodable test cube, In this case, it is not possible to encode the test cube with this particular linear decompressor. In order to handle unencodable test cubes, a simple way is just to bypass the decompressor when applying those test cubes. Another approach is to restart the ATPG to find a different test cube that is encodable. A third approach is to use more free variables when decompressing the test cubes, which can make it easier to solve the linear equation. Generally, it is very unlikely to be able to encode a test cube as it has more specified bits than the number of free variables. In other words, when the number of free variables is sufficiently larger than the number of specified bits, the probability of not being able to encode the test cube becomes negligibly small. For example, if the number of free variables is 20 more than the number of specified bits, then the probability of not finding a solution is less than 10–6. The encoding efficiency, for linear decompressors can be defined as follows:

### (Specified Bits in Test Set)/(Bits Stored on Tester)

The optimality of encoding efficiency is 1. However, it is not possible to achieve higher than an encoding efficiency of 1 because there are normally more free variables than specified bits.

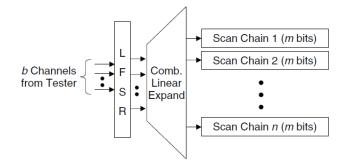

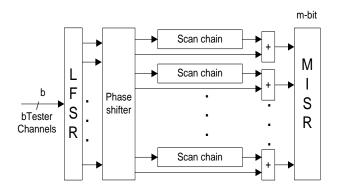

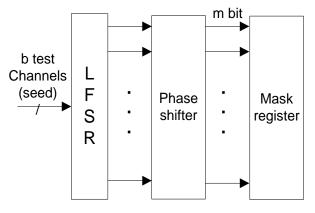

Since a sequential linear decompressor allows free variables from earlier clock cycles to be used when encoding a scan slice in the current clock cycle, it can provide much more flexibility than combinational decompressors and solve the problem of the worst-case most highly specified scan slices limiting the overall compression. In other words, the more flip-flops that are used in the sequential linear decompressor were described in [25], [26], and [27], as illustrated in Figure 2.15. There are b channels from the tester that load free variables into LFSR (one of linear finite-state machines), and the following is the combinational linear XOR network that expands the outputs of the LFSR to fill scan chains. In decompressing process for each test cube, the state of the LFSR is first reset and then some initial free variables are loaded to LFSR within a few clock cycles. After that, additional free variables are loaded into the LFSR in each clock cycle. The total number of free variables that are use to fill each test cube is equal to b (q+m), where b is the number of channels from the tester, q is the number of clock cycles used to initially load the LFSR, and m is the length of the longest scan chain.

Figure 2.15 Typical sequential linear decompressor [9]

#### 2.4.3 Broadcast-Scan-Based Schemes

The third kind of test stimulus compression schemes that broadcast the same value to multiple scan chains was first proposed in [28] and [29]. This method has been widely used in many test compression architectures. The advantage is the same pattern can be extended to multiple circuits as illustrated in Figure 2.16. The problem is how to guide the ATPG tool to generate the patterns to be shared. Generally, the inputs here include the primary inputs as

well as the pseudo-primary inputs.

Figure 2.16 Broadcasting to scan chains driving independent circuits [9]

Since one test vector can detect a fault in a stand-alone circuit then it will still be possible to apply this vector to detect the fault in the broadcast structure, the main benefit of broadcast scan for independent circuits is that all faults that are detectable in all original circuits will also be detectable with the broadcast structure. Thus, the broadcast scan method will not affect the fault coverage if all circuits are independent. Moreover, broadcast scan can also be applied to a single circuit if all subcircuits driven by the scan chains are independent.

After the test stimulus data has been applied to CUT, the response data requires to be shifted out for compaction. The compaction technique is described next.

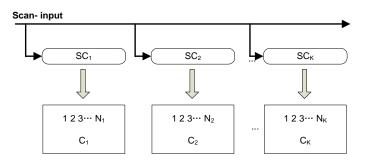

## 2.5 Test Response Compaction

Due to a large number of scan cells in complex designs, the test data volume would be large and the test time would be long. A common way for reducing test data volume and test time is to break original scan chains into a larger number of shorter scan chains, and then use a smaller number of ATE channels to specify inputs stimulus and observe output responses. Figure 2.17 shows the architecture for input stimulus compression and output response compaction in a scan-based design. It contains total k test channels from ATE for input stimulus, where (k<n). After compaction, the total bits are m, which is greatly less than the total number of scan chains (n). The output response compaction can generate a "signature" for output responses, the signature then can be observed through a limited number of scan chains with a limited number of

ATE channels, researchers have recently worked on input stimulus compression and output response compaction.

Figure 2.17 Compression scheme for scan-based designs

Test response compaction is performed at the outputs of the scan chains. The test data after compaction must be transferred back to the tester. Unlike lossless for test data in stimulus compression, the test responses in test compaction can be lossy. The compaction techniques generally are classified into three categories: space compaction, time compaction, and mixed time and space compaction.

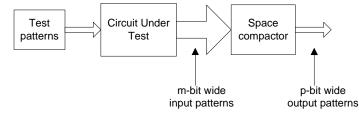

### 2.5.1 Space Compaction

The space compaction can be expressed as a linear function of the input vector

X and the output vector Y

$$\mathbf{Y} = \boldsymbol{\varphi}(\mathbf{X})$$

where X is an m-bit input vector and Y is an p-bit output vector, p<m, asillustrated in Figure 2.18.

Figure 2.18 Space compaction schemes [9]

Figure 2.19 is a simple example to show the space compactor for compacting 4

( m=4 ) scan chains of the circuit under test to 1(p=1) output, where the combinational circuit consists of the network of XOR gates.

Figure 2.19 Basic space compactor structure

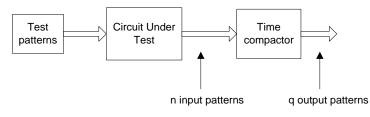

## 2.5.2 Time Compaction

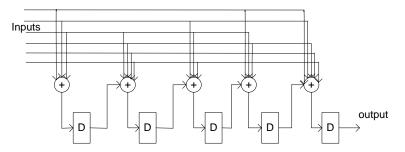

Different from space compactor using combinational logic, the time compactor uses sequential logic. A time compactor compacts n input patterns to q output patterns (where q < n), as illustrated in Figure 2.20. Once time compactor is applied, no X's from circuit under test is allowed to reach the compactor.

Figure 2.20 Time compaction schemes [9]

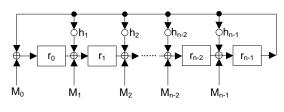

The most widely used time compactor is the MISR. The Figure 2.21 demonstrates the n-stage MISR. The structure of the n-stage MISR can be expressed by a specified characteristic polynomial of degree n, f(x), the symbol  $h_i$  can be set either 1 or 0 based on the existence or absence of the feedback path, where:

$$F(x) = 1 + h_1 x + h_2 x^2 + \dots + h_{n-1} x^{n-1} + x^n$$

Figure 2.21 An n-stage MISR [9]

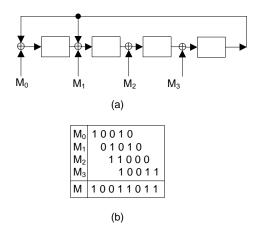

Take an example for the four-stage MISR applying  $f(x) = 1+x+x^4$ , as illustrated in Figure 2.22(a). Set  $M_0$ = {10010},  $M_1$ = {01010},  $M_2$ = {11000}, and  $M_3$ = {10011}. After calculating by the formula  $M(x) = M_0(x) + xM_1(x) + x^2M_2(x) + x^3M_3(x)$ , it can get  $M(x) = 1+x^3+x^4+x^6+x^7$  or M= {10011011}, as shown in Figure 2.22(b). Finally, the signature R is represented by the rightmost four bits of the M sequence. Hence, R= {1011}.

Figure 2.22 An equivalent *M* sequence for four-stage MISR [9]

In this example, there are totally four input patterns (n=4) such as  $M_0$ ,  $M_1$ ,  $M_2$ , and  $M_3$ . After compaction, there is only one output pattern (q=1) R.

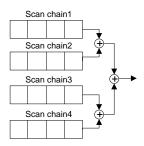

# 2.5.3 Finite Memory Compaction

In this section, finite memory compaction is introduced, which combines the advantages of time compaction and space compaction. Many finite memory compactors have been proposed such as OPMISR [30], convolutional compactor [31], and q-compactor [32] [33] [34].

Figure 2.23 shows a simple example about the basic structure of a q-compactor, including six inputs coming from scan chains and one output, where each flip-flop is

connected to the corresponding output of XOR network. It shows that every error in a scan cell can reach storage elements and then outputs in several possible ways. Since the q-compactor does not have feedback path, any error can be shifted out for comparing with the expected data after at most five cycles.

Figure 2.23 An example q-compactor with single output [9]

The list three types of compactor is very efficient for output compaction. However, once X's occur in output responses, the fault coverage may lost due to error masking, which is described in next section.

#### 2.6 Error Masking

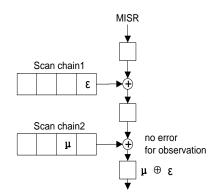

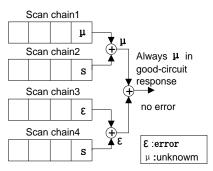

Once these X's are introduced into the output response data, the performance of the test compression schemes can be significantly degraded. For the class of output compactors called time compactors, MISRs for example, once an unknown is introduced, the signature quickly becomes corrupted and must be reset, that means no error can be observed. For example, the MISR and two scan chain in Figure 2.24. The scan chain 1 contains one error in first cycle and scan chain 2 contains an X in second cycle respectively, after two cycles the  $\varepsilon$  and  $\mu$  are XORed together in MISR bit, then the error is corrupted.

Figure 2.24 Error masking in MISR

When the scan-out responses come to output compactors, the scan-out responses are compacted by XOR gates. However, an error response may not be observed due to unknown-induced error masking. An error means a response different from the good circuit response. An X means the value in response is not determined in simulation. Take an example for space compactor in Figure 2.25, an error and an X are represented by ' $\varepsilon$ ' and ' $\mu$ ', respectively, and 's' means don't care bit. The unknown and error can be propagate to the output of XOR operation, for example the result of XOR operation between ' $\mu$ ' in scan chain 1 and 's' in scan chain 2 is ' $\mu$ '. The error cannot be observed after XOR operation with an X, and the second stage of XOR operation shows the result of XOR operation between ' $\varepsilon$ ' and ' $\mu$ '. This is called unknown-induced error masking which happens when there is an X along with some errors at the inputs of the compactor. Under such a situation, the good-circuit response at the compactor output is X, Thus, no error can be observed.

Figure 2.25 Error masking in space compactor

Since the structure of the finite memory compactors is adding some memory elements in the space compactor, the compaction schemes obtained by combining time and space

dimensions, so the error masking in finite memory compactors happens in both situation of time compactor and space compactor.

# 2.7 Summary

In this chapter, the overview of VLSI testing technology development is provided and the main challenge of VLSI testing is discussed. In order to illustrate the problem statement clearly, the whole picture is draw in this area including the basic DFT concepts, scan design and test compression techniques. As shown in this chapter, the presence of X's in test responses can greatly degrade the output compaction due to the error masking. In order to handle this problem, several efficient schemes are proposed in the next chapter.

# **CHAPTER 3**

# **RELATED SCHEMES FOR HANDLING UNKNOWN VALUES**

#### 3.1 Introduction of Schemes for Handling X's

Scan design has become main stream for complex digital circuits in test industry. For the test compression, the main goal is to achieve high test quality with lower test overhead. However, the presence of X's in test streams can largely degrade the efficiency of compression during test mode. To reduce the impact of X's, a large number of schemes for handling X's have been developed in recent years. The basic methods are X-blocking, X-masking and X-tolerant.

During response capture, the generated X's can be blocked from reaching the scan cell. One way is to identify X sources and add additional DFT logic to fix the X sources by adding additional test points [35]. Another way is to block the X's from reaching the scan cells by careful test pattern generation. The approach in [36] is to identify the X-candidates and to generate control vectors for reducing the number of X's in the scan response. X-blocking can ensure that no X's will be observed. However, it does not provide a means for observing faults, which can cause fault coverage lost. In addition, the approach in [36] is not compatible with the test data compression technique.

As the X-blocking technique may cause fault coverage lost and it does add area overhead and may impact delay due to the inserted logic, the X's can also be masked off right before the response compactor [37-40]. The X-masking technique can be easily implemented as it just adds the X-masking logic in front of compactor. It does cause additional hardware overhead. However, it does not cause any circuit delay during the test.

Meanwhile, the X's can be tolerated during the compaction of the test response. The X-tolerant technique is used to design a compactor which can guarantee the errors are detected even in the presence of X's in the same clock cycle. The main advantage is it does not require any additional hardware for X-masking logic and does not degrade the system performance during normal operation. For the space compactors, it utilizes XOR gates to compact test response coming from N scan chains  $\{0, 1, X\}^N$  into a compacted observable test response with Q outputs  $\{0,1,X\}^Q$  for each scan cycle, where N > Q. The following section lists several related schemes for handling X's in recent years.

### 3.2 X-masking Techniques

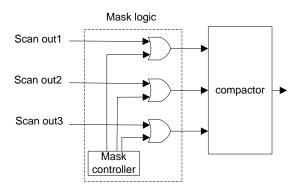

As mentioned earlier, the X-masking techniques are applied to mask X's before the X's coming to response compactor. Figure 3.1 shows a general structure of X-masking circuit with three scan outs. It shows that the mask controller can apply a logic value '1' for any scan output to mask off X's in scan output responses. Notice that the mask date can be generated for each scan cycle and it can be stored in compressed format.

Figure 3.1 A simple X-masking circuit

Many schemes for X-masking have been proposed. In this section, some important X-masking schemes are list, including conventional LFSR X-masking, reiterative X-masking, and X-masking by use of a Hierarchical-Configurable-Mask-Register (HCMR).

### 3.2.1 Conventional LFSR X-masking

The conventional LFSR X-masking is wildly used scheme which is described in [13]. It creates a mask for every scan slice to ensure that all X's in each scan slice get masked, and all d's remain unmasked, where d records a value that is required to be observed for the detection of one or more faults. The basic architecture of this technique is shown in Figure 3.2. We can see the LFSR is used to drive scan chains and create the mask data from the phase shifter as well. The compressed mask data stored on the ATE is expanded through LFSR for each scan slice. Since the ATE has to store enough mask data to create a mask for every slice, amounts of mask data are required.

Figure 3.2 Architecture of conventional LFSR X-masking [13]

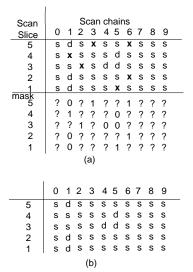

Figure 3.3a shows the basic operation for conventional LFSR X-masking. For an interval of each scan slice, the mask bit is given for each scan cell. The mask bit can be set to '1' (masked) if X is present in a scan cell; the mask bit can be set to '0' (unmasked) if d is present; if there is neither of X and d in a scan cell, the mask bit can be set to '?'(don't care). The results are shown in Figure 3.3b where none of X's is left and all d's remain after masking.

Figure 3.3 Conventional LFSR X-Masking Example

As the conventional LFSR X-masking scheme creates X-mask for each scan cell, it ensures that all X's can be masked off, but the number of mask bit is huge. In order to reduce the mask bit overhead, a further research is given in next section.

# 3.2.2 Reiterative X-masking

The reiterative X-masking technique can create a mask for more than one scan slice, as described in [14]. This technique lists two efficient methods, including variable reiterative LFSR X-Masking and hybrid X-masking approach based on different number of X's in test response.

### 3.2.2.1 Variable Reiterative X-masking

The variable reiterative LFSR X-Masking scheme applies a mask for a number of scan slices. It also ensure that all X's in each scan slice get masked and all d's get unmasked, but less number of mask data are used by finding a mask that is usable for a varying number of adjacent scan slices. The structure of this approach is shown in Figure 3.4. The decompressor is used to load scan chains and create mask data every *i* clock cycles.

Figure 3.4 Structure of variable reiterative LFSR X-Masking [14]

The way for finding a solution of the masks for a given pattern is list as

follow:

- 1) First find the location of all the *d* and *X* bits.

- Apply a mask for the first scan slice at the beginning of the current interval. For example, the scan slice 1 in Figure 3.5a gets an X in position 6, so the mask bit for this position is '1'. As positions 1 and 2 in scan slice 1 are d's, so the mask bits for those positions are '0's.

- Add the interval by one to load the current mask. For scan slice 2, bit position 5 gets a *d*, so the mask bit for this position is set to '0'. Since position 4 gets an X, the mask bit is '1'.

- 4) Rerun step 3 until at least one mask bit position gets a conflict. If the conflict happens, the current scan slice needs to be set the beginning of a new interval. Then skip to step 2. For example, when load scan slice 5 to the current interval, an X occurs in bit positions 2 and 5, which can cause a conflict. Finally, M1 creates the mask for scan slices 1-4, and M2 is for 5-7. Figure 3.5b shows the results after masking.

|   | Coor          | Scan chains |   |   |     |   |    |   |   |   |   |   |

|---|---------------|-------------|---|---|-----|---|----|---|---|---|---|---|

|   | Scan<br>Slice | 0           | 1 | 2 | 3   | 4 |    | 5 | 6 | 7 | 8 | 9 |

|   | 7             | s           | d | S | s   | s | [] | x | s | s | S | s |

|   | 6             | s           | s | s | d   | d | :  | s | d | s | х | s |

|   | 5             | S           | d | x | s   | S |    | x | s | s | s | s |

|   | 4             | s           | s | s | d   | S |    | d | S | s | s | s |

|   | 3             | S           | s | d | s   | s | :  | s | х | s | s | s |

|   | 2             | s           | s | s | s   | x |    | d | s | s | s | s |

|   | 1             | s           | d | d | s   | s |    | s | x | s | s | s |

| - | M2            | ?           | 0 | 1 | 0   | 0 |    | 1 | 0 | ? | 1 | ? |

|   | M1            | ?           | 0 | 0 | 0   | 1 | (  | 0 | 1 | ? | ? | ? |

|   | l             |             |   |   |     |   |    |   |   |   |   |   |

|   |               |             |   |   | (a) |   |    |   |   |   |   |   |

|   |               | 0           | 1 | 2 | 3   | 4 | 5  | 6 | 7 | 8 | 9 |   |

|   | 7             | S           | d | S | s   | s | S  | S | S | S | s |   |

|   | 6             | s           | s | s | d   | d | s  | d | s | s | s |   |

|   | 5             | s           | d | s | s   | s | s  | s | s | s | s |   |

|   | 4             | s           | s | s | d   | s | d  | s | s | s | s |   |

|   | 3             | s           | s | d | s   | s | s  | s | s | s | s |   |

|   | 2             | s           | s | s | s   | s | d  | s | s | s | s |   |

|   | 1             | s           | d | d | s   | s | s  | s | s | s | s |   |

|   |               |             |   |   | (b) |   |    |   |   |   |   |   |

Figure 3.5 Variable Reiterative LFSR X-Masking Example [14]

As it can reuse masks for multiple adjacent scan slices, the amount of mask data stored on the ATE can be reduced significantly. Thus, the output data compression can be greatly improved. However, this approach is efficient just for small numbers of X's. When the number of X's gets large, a hybrid X-masking is proposed in next section.

# 3.2.2.2 Hybrid X-masking Approach

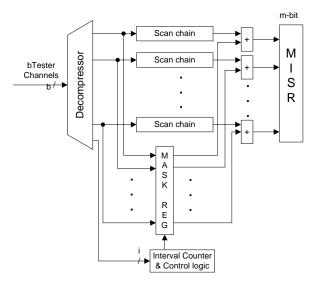

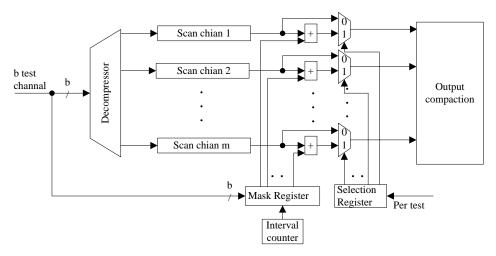

Hybrid X-masking approach uses fixed-interval reiterative X-masking combined with conventional LFSR X-masking. The primary advantage of the reiterative X-masking logic is to mask all of the easy to mask X's by reusing masks for many scan slices, and the conventional LFSR X-masking can handles the rest. The structure of this approach is shown in Figure 3.6.

Figure 3.6 Hybrid X-Masking architecture [14]

In this Figure, the decompressor is used to drive scan chains and the LFSR with phase shifter is applied to generate the mask bits. For m scan chains, the hardware architecture consists of an m-bit masking register, an i-bit interval counter, 2m OR gates. This LFSR is not only used to generate the mask for each slice for the conventional LFSR X-masking part of this approach, but also generate the mask bits to load the mask register for the reiterative

X-masking part. Reiterative LFSR X-masking logic is designed to reuse a mask data when adjacent scan slices got X's mask X's for a number of scan slices and keep all d's. In order to keep the overhead of storing the mask data small, a reseedable LFSR is used to encode just the X and d bits. The interval counter is loaded one time at the beginning of the test from the b tester channels. The interval counter counts down the number of shift cycles until the interval counter becomes zero. Once that happens, a new mask is loaded into the mask register and the interval counter is returned to the initial value.

The operation for fixed-interval reiterative X-masking is shown in Figure 3.7a, For an interval of five scan slices, mask bits can be set to '1' (masked) in scan chains 2, 3, and 6 if X's are present without d's, and mask bits can be set to '0' (unmasked) in scan chains 1, 4, and 5 since d's are present. If there are neither of X's and d's in scan chains 0, 7, 8, and 9, the mask bits is set to '?'(don't care). The results are shown in Figure 3.7b where in two X's are left in scan chains 1 and 5, which can be handled by conventional X-masking logic. Note that the size of the interval counter determines the overall effectiveness of this hybrid approach. If the size of interval counter gets smaller, the remaining of X's usually presents less, but more mask bits are required, otherwise the mask bits will be smaller. Thus, the minimum size of interval counter has been determined and can be re-loaded in different test patterns.

| Scan  | Scan Chains |   |       |   |     |   |      |   |   |   |   |

|-------|-------------|---|-------|---|-----|---|------|---|---|---|---|

| slice | 0           | 1 | 2     | 3 | 4   | 5 | 6    | 7 | 8 | 9 |   |

| 5     | s           | d | S     | x | s   | s | x    | s | s | s |   |

| 4     |             |   | 10101 |   |     |   | 1333 |   |   |   |   |

|       | s           | x | S     | S | S   | d | S    | s | s | s |   |

| 3     | s           | s | x     | S | d   | d | S    | s | s | s |   |

| 2     | s           | d | S     | S | s   | s | x    | s | s | s |   |

| 1     | s           | d | s     | s | s   | х | s    | s | S | s |   |

| Mask  | ?           | 0 | 1     | 1 | 0   | 0 | 1    | ? | ? | ? | _ |

|       |             |   |       |   | (a) |   |      |   |   |   |   |

|       | 0           | 1 | 2     | 3 | 4   | 5 | 6    | 7 | 8 | 9 |   |

| 5     | s           | d | s     | s | s   | s | s    | s | s | s |   |

| 4     | s           | х | s     | s | s   | d | s    | s | s | s |   |

| 3     | s           | s | s     | s | d   | d | s    | s | s | s |   |

| 2     | s           | d | s     | s | s   | s | s    | s | s | s |   |

| _ 1 _ | s           | d | s     | s | s   | x | s    | s | s | s | _ |

| (b)   |             |   |       |   |     |   |      |   |   |   |   |

Figure 3.7 Reiterative X-Masking Example [14]

Comparing conventional LFSR X-masking, this approach can provide

significant reduction of mask bits overhead as masks are reused for multiple scan slices. Moreover, this approach handles the X's into two cases: small number of X's and large number of X's. Using Variable Reiterative LFSR X-masking can significantly increase the amount of compression for smaller numbers of X's. When the number of X's gets large, then a hybrid approach is applied. In order to mask X's more specifically, another X-masking scheme called hierarchical configurable mask register is proposed to apply optimal mask bit based on the different distribution of X's in the next.

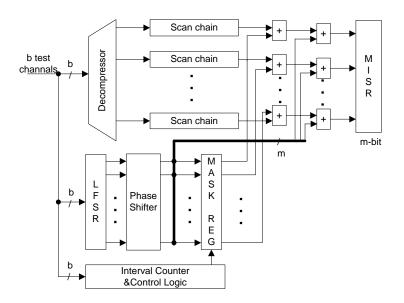

# 3.2.3 Hierarchically Configurable Register

In this section, a hierarchical method is proposed in [41] for X-masking by use of a HCMR. The main idea of this approach is to select a subset of l of the k scan chains first. Then an optimized X-mask is applied only for selected l scan chains in each test pattern. A single control signal is used to determine whether the X-mask will be applied or not for every scan cycle. After the X-mask operation, the remaining X-values can be tolerated by an X-tolerant compactor. The basic implement of this approach is described as follow.

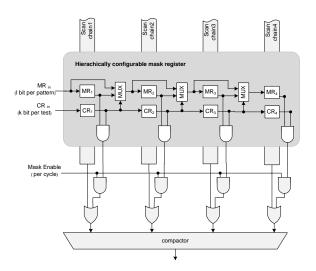

#### 3.2.3.1 Implement of Hierarchical Configurable Mask Register

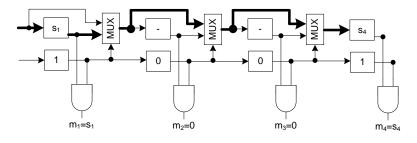

Figure 3.8 Structure of hierarchical configurable mask register [41]

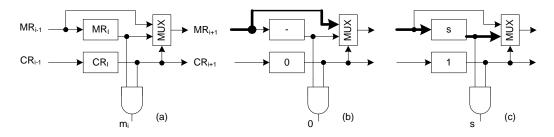

The hardware structure of the proposed *HCMR* is described in Figure 3.8. There are four (k=4) scan chains, and the HCMR have two separate shift register Configuration-Register (CR) and Mask-Register (MR) in it. The *CR* consists of flip-flops *CR*<sub>1</sub>,...,*CR*<sub>k</sub> and *MR* consists of flip-flops *MR*<sub>1</sub>,...,*MR*<sub>k</sub>. A multiplexer *MUX*<sub>i</sub> is connected to the every output of *MR*<sub>i</sub>. The *Mask Enable* signal is used to allow the activation of X-mask. Once *Mask Enable* signal is active, the selected scan chains are allowed to be masked based on the values stored in *MR*.