# เป็นหนังสือภาษาอังกฤษ

รายงานวิจัยฉบับสมบูรณ์

โครงการ

วงจรกรองแบบเวลาต่อเนื่องสำหรับระบบสื่อสารแบบไร้สายโดยใช้รูปแบบของทรานคอนดัคเตอร์

(แบบป้อนกลับกระแส) -ตัวเก็บประจุ

High-Order Continuous-Time Filters employing Current-Feedback Transconductor-Capacitor

Structure in CMOS Technology for Wireless Communications

โดย

ภาณุมาส คำสัตย์ และคณะ

#### **Table of Contents**

| Abstract                                                                                                            |       |

|---------------------------------------------------------------------------------------------------------------------|-------|

| บทคัดย่อ                                                                                                            | 7     |

| บทสรุปสำหรับผู้บริหาร                                                                                               | 8     |

| Executive Summary                                                                                                   | 8     |

| Acknowledgement                                                                                                     | 9     |

| Chapter 1                                                                                                           | 11    |

| HIGHLY-LINEAR, CURRENT-FEEDBACK RESISTIVE SOURCE-DEGENERATED MOS TRANSCONDUCTO                                      | )R 11 |

| 1.1 Introduction                                                                                                    | 11    |

| 1.2 Priciple of Current-Feedback Source-Degenerated Transconductor                                                  | 11    |

| 1.3 Proposed Current-Feedback Source-Degenerated Transconductors                                                    | 13    |

| 1.4 Simulation Results                                                                                              | 16    |

| 1.5 Conclusion                                                                                                      | 17    |

| References                                                                                                          | 19    |

| Chapter 2                                                                                                           | 20    |

| A 1.8-V CMOS Polyphase Filter for Dual-Mode Bluetooth/ZigBee Transceiver                                            | 20    |

| 2.1 INTRODUCTION                                                                                                    | 20    |

| 2.2 REVIEW OF COMPLEX FILTERS                                                                                       | 21    |

| 2.3 TRANSCONDUCTOR CIRCUIT                                                                                          | 22    |

| 2.4 FILTER DESIGN                                                                                                   | 24    |

| 2.5 SIMULATION RESULTS                                                                                              | 26    |

| 2.6 CONCLUSION                                                                                                      | 30    |

| Chapter 3                                                                                                           | 33    |

| Application of Reverse-Active $npn$ s for Compact, Wide-Tuning $f_{_{ m T}}$ -Integration-based Filters in SiGe HBT |       |

| BICMOS Technology                                                                                                   | 33    |

| 3.1. Introduction                                                                                                   | 33    |

| 3.2. f <sub>t</sub> -Integration Principle                                                                          | 34    |

| 3.3. Wide-Tuning f <sub>r</sub> -Integrator Design in SiGe HBT BiCMOS Technology                                    | 34    |

| 3.4. Simulation Results                                                                                             | 37    |

| 3.5. Conclusion                                                                                                     | 41    |

| Chapter 4                                                                                                           | 43    |

| High-Gain Current Amplifiers for Low-Power MOSFET-C Filters                                                         | 43    |

| 4.1 Introduction                                                                                                    | 43    |

| 1.2 MOSFET-C Integrator Employing Current Amplifier                                                                 | 43    |

| 4.3 Proposed High-Gain Current Amplifiers for MOSFET-C or Active-RC Filters                   | 45 |

|-----------------------------------------------------------------------------------------------|----|

| 4.4 Second-order Filter and Biasing Technique                                                 | 46 |

| 4.5 Simulation Results                                                                        | 49 |

| 4.6 Conclusion                                                                                | 53 |

| Chapter 5                                                                                     | 55 |

| Compact Operational Transconductance Amplifiers for Low-Voltage MOSFET-C Filters              | 55 |

| 5.1 Introduction                                                                              | 55 |

| 5.2 Circuit Description                                                                       | 55 |

| 5.3 Simulation Results                                                                        | 58 |

| 5.4 Summary                                                                                   | 61 |

| 5.5 References                                                                                | 61 |

| Chapter 6                                                                                     | 67 |

| Structure of the Complex Elliptic Gm-C Filters Suitable for Fully-Differential Implementation | 67 |

| 6.1 Introduction                                                                              | 67 |

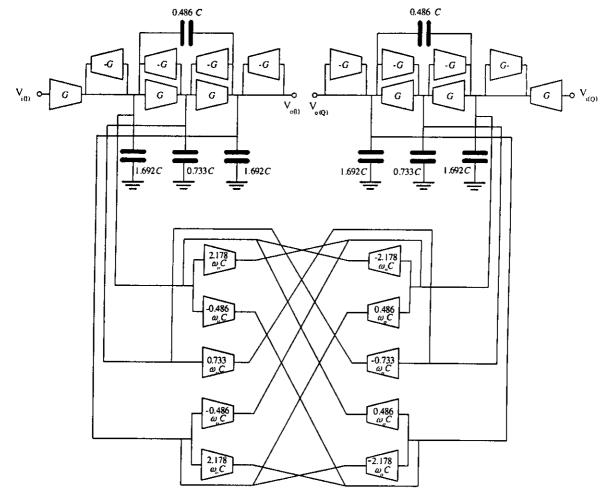

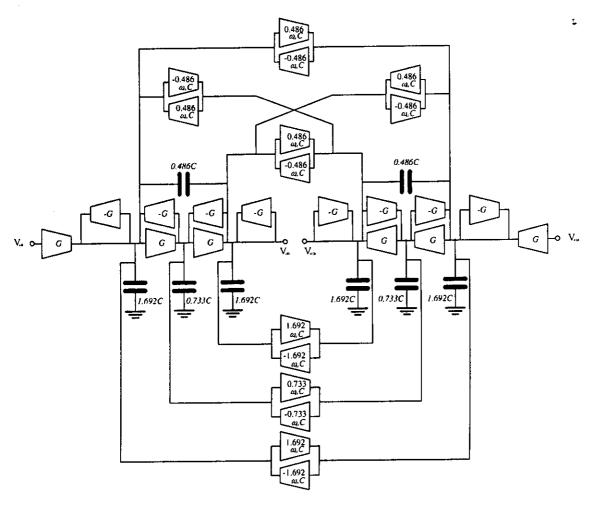

| 6.2 COMPLEXIFICATION OF GM-C FILTER USING STATE-SPACE TECHNIQUE                               | 70 |

| 6.3 Complexification of Gm-C Filter by Element Substitution Technique                         | 74 |

| 6.4 Design Example                                                                            | 76 |

| 6.5 Transistor-Level Simulation                                                               | 78 |

| 8.4 Summary                                                                                   | 84 |

| 8.5 References                                                                                | 85 |

| Chapter 7                                                                                     | 86 |

| Conclusion and Future Works                                                                   | 86 |

| 7.1 Conclusion                                                                                | 86 |

| 7.2 Future Works                                                                              | 86 |

| Publications                                                                                  | 88 |

| Appendix                                                                                      | 89 |

•

#### **ABSTRACT**

Investigation on various aspects of integrated filter design in CMOS technology under low supply voltage is presented.

A resistive source-degeneration CMOS transconductor with excellent linearity utilizing current-feedback has been described. The technique adds minimum complexity (just two or four additional transistors) to enhance linearity without extra current consumption, in other words high transconductance/current efficiency of an ordinary source degeneration transconductor is preserved but with superior linearity performance. The transconductance's polarity inversion of Caprio's quad has also been solved by adding another cross-coupling transistor pair.

A 1.8V CMOS dual-mode fifth-order polyphase GmC filter for Bluetooth/ZigBee transceiver has been designed. The complex bandpass filter is based on Gm-C filter structure with appropriate crossing transconductors to shift lowpass response to the required IF frequencies. It deploys a simple source degeneration transconductor integrated with a network, which could simultaneously provide common-mode stability and dc gain enhancement.

High-gain current amplifiers have been successfully employed as an alternative active building block to conventional operational amplifiers or operational transconductance amplifier in MOSFET-C and active-RC filters. The second-order filters employing the proposed current amplifiers render better linearity performance over the conventional folded-cascode OTA.

A compact OTA suitable for low voltage filter implementations has been developed. The circuit relies primarily on the feed-forward class AB output stage that features low supply operation and common-mode rejection at no cost to transconductance/bias-current efficiency. It is envisaged that the feed-forward output configuration could be applied to current-mode circuits in general or any other circuits with output current variables, such as transconductor (G<sub>m</sub>), current conveyor etc. Verified through extensive simulation, it was demonstrated that a low supply voltage filter with a competitive FoM performance at small complexity is entirely viable with the use of the OTA structure.

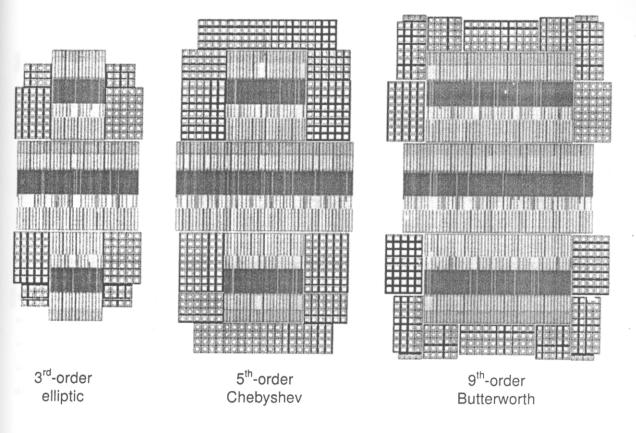

Two different methods have been presented, basing on state-space and element substitution, to transform the real Gm-C filters with floating capacitors into the corresponding complex Gm-C filters. The resulting complex filter structure is suitable for fully-differential implementation using widely-used fully-differential transconductors. To demonstrate the proposed method, the fully-differential complex Gm-C filter was realized from the 3rd-order elliptic Gm-C filter. It was found that with the same frequency specifications, the elliptic complex filter derived from the proposed method outperforms the Butterworth and Chebyshev complex filters in terms of noise, linearity, area, and power consumption.

### บทคัดย่อ

โครงการวิจัยนี้ได้ทำงานศึกษาเทคนิคต่าง ๆที่เป็นประโยชน์ในการออกแบบวงจรกรองความถี่ในเทคโนโลยี ซึมอสสำหรับใช้งานภายใต้ไฟเลี้ยงต่ำ

วงจรทรานส์คอนดัดเตอร์แบบซอสดีเจนเนอเรชั่นที่ใช้ตัวด้านทานและมีความเป็นเชิงเส้นสูงโดยอาศัยหลักการ ป้อนกลับซึ่งส่งผลในการกำจัดความไม่เป็นเชิงเส้นของทรานซิสเตอร์และไม่มีการใช้กำลังงานเพิ่มเมื่อเทียบกับ เทคนิคเดิม นอกจากนี้ได้มีการเสริมวงจรเพิ่มเพื่อทำให้ขั้วของวงจรเป็นบวกเสมอเพื่อป้องกันปัญหา เสถียรภาพของวงจรเมื่อนำไปใช้ในวงจรกรอง

ได้ทำการออกแบบวงจรกรองเชิงซ้อนโดยใช้เทคนิคทรานส์คอนดักเตอร์-ตัวเก็บประจุสาหรับภาครับของ ระบบบลูทูธและชิกบี วงจรกรองดังกล่าวเป็นแบบเซพบีเซพลำดับห้าและทำงานภายใต้ไฟเลี้ยง 1.8 โวลต์ ได้มี การใช้เทคนิคเพื่อรับรองเสถียรภาพสำหรับโหมดร่วมของวงจรพร้อมกับการเพิ่มอัตราขยาย

ได้ทำการออกแบบวงจรขยายกระแสที่มีอัตราขยายสูงสำหรับการออกแบบวงจรกรองแบบมอสเฟต-ซีหรือแบบ แอคทีฟ-ตัวต้านทาน/ตัวเก็บประจุ ซึ่งวงจรดังกล่าวทำหน้าที่แทนออปแอมป์หรือวงจรขยายทรานส์คอนดัค แตนซ์ (โอทีเอ) ได้มีการเปรียบเทียบประสิทธิภาพการทำงานกับวงจรโอทีเอแบบพับดั้งเดิมและพบว่าวงจรที่ นำเสนอให้วงจรกรองที่มีความเป็นเชิงเส้นสูงกว่า

มีการออกแบบโอทีเอขนาดเล็กซึ่งเหมาะสำหรับวงจรกรองที่ใช้ไฟเลี้ยงต่ำ วงจรดังกล่าวอาศัยหลักการป้อนไป ด้านหน้าซึ่งทำงานในแบบคลาสเอบี โครงสร้างดังกล่าวสามารถขจัดสัญญาณโหมดร่วมได้โดยไม่สูญเสีย อัตราชยายและไม่มีความจำเป็นต้องสูญเสียกำลังงานเพิ่ม ซึ่งเทคนิคดังกล่าวสามารถนำไปประยุกด์ใช้กับวงจร ที่มีกระแสเป็นตัวแปรด้านออกเช่น ทรานส์คอนดัดเตอร์ วงจรสายพานกระแส

นำเสนอสองวิธีการสำหรับการออกแบบวงจรกรองเชิงซ้อนที่แปลงมาจากดันแบบวงจรกรองผ่านความถี่ต่ำแบ บทรานส์คอนดักเตอร์-ตัวเก็บประจุที่มีตัวเก็บประจุลอยเช่นแบบอีลิปติกคือวิธีเสตท-เสปซและวิธีแทนตัว อุปกรณ์ เทคนิคที่นำเสนอเหมาะสำหรับวงจรผลต่างแบบสมดุลซึ่งสามารถนำทรานส์คอนดักเตอร์ทั่ว ๆไปมา ใช้ได้ ตัวอย่างการออกแบบได้นำเสนอผ่านวงจรอีลิปติกอันดับสามซึ่งก็ได้แสดงให้เห็นว่าตัวยประสิทธิภาพการ กรองที่เท่าเทียมกันวงจรที่นำเสนอสามารถประหยัดกำลังงาน พื้นที่ซิลิกอนได้ดีกว่า มีสัญญาณรบกวนต่ำกว่า มีความเป็นเชิงเส้นสูงกว่า เมื่อเทียบกับวงจรที่สร้างมาจากต้นแบบเซฟบีเซฟอันดับห้าและวงจรบัดเตอร์เวิร์ช อันดับเก้า

## บทสรุปสำหรับผู้บริหาร

โครงการวิจัยนี้นำเสนอเทคนิคการออกแบบวงจรสำหรับวงจรกรองความถี่ในเทคโนโลยีซีมอสสำหรับ ระบบสื่อสารไร้สายที่ใช้ไฟเลี้ยงต่ำ เทคโนโลยีที่ใช้มีขนาด 0.18 ไมครอนและมอสทราสซิสเตอร์มีแรงดันขีดเริ่ม ประมาณ 0.45โวลต์ เทคนิคที่คิดคันนี้ได้ศึกษาสำหรับการประยุกต์ใช้กับวงจรกรองแบบทรานส์คอนดัคเตอร์- ตัวเก็บประจุและแบบแอคทีฟ-ตัวด้านทาน/ตัวเก็บประจุ สิ่งที่ได้นำเสนอนั้นคือ วงจรทรานส์คอนดัคเตอร์ วงจรขยายทรานส์คอนดัคแตนซ์ปฏิบัติการ (โอทีเอ) วงจรขยายกระแสปฏิบัติการ การออกแบบวงจรกรอง เชิงซ้อน การนำเสนอเทคนิคการป้อนไปด้านหน้าแบบโหมดผลต่างและโหมดร่วมซึ่งทำงานในคลาสเอบี

#### **Executive Summary**

This research presents various design techniques for integrated filters targeted for modern wireless communication chip operating under a low-voltage supply. The proposed techniques have been studied for Gm-C and active-RC filtering structures. And this renders useful circuit techniques for transconductors, operational transconductance amplifier (OTA), operational current amplifier, complex filters, and dual-mode (differential-mode and common-mode) feedforward technique working in class-AB.

# HIGHLY-LINEAR, CURRENT-FEEDBACK RESISTIVE SOURCE-DEGENERATED MOS TRANSCONDUCTOR

#### 1.1 Introduction

Transconductors or voltage-to-current converters  $G_{\mathrm{m}}$  are fundamental building blocks in analog circuit applications ranging from wideband amplifiers, high-frequency continuous-time filters, highspeed continuous-time delta sigma A/D converters, and other interface circuits. In many of these applications, highly-linear and large dynamic range transconductors are essential because they usually determine overall performance of the whole circuits and systems. Numerous circuit techniques have been proposed to improve the linearity performance of the transconductor [1.1]-[1.6] and, interestingly, they all can be classified as variants of the classical source-degeneration technique using passive resistors. These resistive source degeneration transconductors can be further divided into two main categories, namely (a) those based on the 'super  $G_{m}$ ' arrangement in which a negative voltage feedback loop formed by a high-gain voltage amplifier [1.1]-[1.3] and (b) those based upon device's non-linearity cancellation by utilizing positive current feedback [1.4]-[1.6]. In this literature, a compact, highly-linear resistive CMOS source-degeneration transconductor based upon an alternative current-feedback (CF) structure will be presented. Unlike many previously reported linear resistor based transconductors, the proposed  $G_m$ 's require only a small number of extra transistors, and therefore the circuit complexity and power consumption are kept at minimum. Comparison between the conventional  $G_m$  and the proposed circuits is provided via simulated performances.

#### 1.2 PRICIPLE OF CURRENT-FEEDBACK SOURCE-DEGENERATED TRANSCONDUCTOR

There are number of previously proposed transconductors which can be considered as a current-feedback resistive emitter/source-degenerated type [1.4]-[1.6]. The Caprio's Quad [1.4] can be viewed as the circuit which has been developed from the translinear principle [1.7]. These  $G_m$ 's employ the same technique of generating equal but opposite voltage variations to counterbalance transistor's

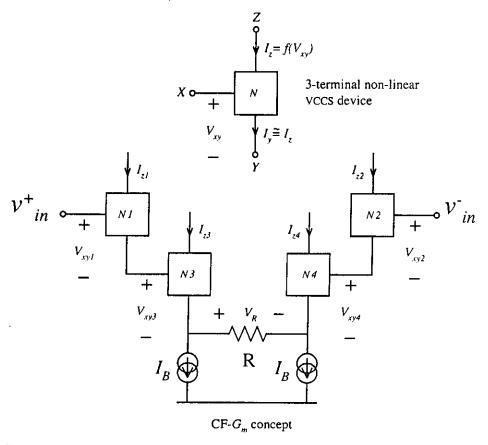

non-idealities resulting in a perfect voltage-to-current conversion by the source-degenerated resistor. The general principle of this current-feedback non-linearity compensated transconductor can be explained by considering the circuit diagram in Fig.1.1. Each rectangular block represents a three-terminal non-linear voltage-controlled current source, for example, it could be either BJT or MOS transistor. By assuming that the relationship between current  $I_z$  (=  $I_y$ ) and voltage  $V_{xy}$  can be expressed by a non-linear function  $f(\cdot)$  such that

Fig.1.1 Conceptual structure of a current-feedback resistive source-degenerated transconductor :

$$I_z = f(V_{xy}) = I_S \exp(V_{xy}/V_T)$$

(1.1)

for a collector current of BJT operating in a forward-active mode with  $V_{xy} = V_{be}$  being a base-emitter voltage, and

$$I_{z} = f(V_{xy}) = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{xy} - V_{TH})^{2}$$

(1.2)

for a drain current of MOS operating in a saturation region with  $V_{xy} = V_{gs}$  being a gate-source voltage. By using KVL, the input voltage can be written as

$$V_{in} = V_{xy1} + V_{xy3} - V_{xy4} - V_{xy2} + V_R$$

$$= f^{-1} (I_{z1}) + f^{-1} (I_{z3}) - f^{-1} (I_{z4}) - f^{-1} (I_{z2}) + V_R$$

(1.3)

It is therefore necessary to eliminate the device's non-linear inverse functions so that the input voltage is linearly transferred to appear across the degenerated resistor  $R_1$ , i.e.,  $V_{in} = V_R$ . This can easily be accomplished by setting  $I_{z1} = I_{z4}$  and  $I_{z2} = I_{z3}$  which can be achieved by injecting feedback currents  $I_{z4}$  and  $I_{z3}$  into Y nodes of devices N1 and N2 respectively. Moreover, if the circuit is a fully balanced structure, the current signal swing of  $I_{z1}$  (=  $I_{z4}$ ) will be equal but in an opposite direction to  $I_{z2}$  (=  $I_{z3}$ ), e.g.,  $I_{z1} = I_B - i_{out}$ ,  $I_{z2} = I_B + i_{out}$ , we would have  $V_{in} = V_R = R \cdot i_{out}$  or  $i_{out} = V_{in}/R$  which is a perfectly linear V-to-1 converter, i.e., a linear transconductor with transconductance  $(g_m)$  of 1/R. In practice, the required feedback current can be provided by means of either cross-coupling [1.4] or current mirroring [1.5], [1.6].

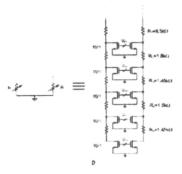

#### 1.3 Proposed Current-Feedback Source-Degenerated Transconductors

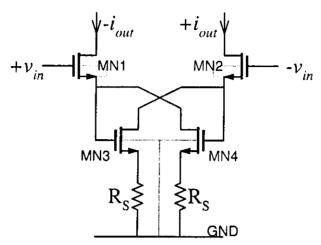

The current-feedback technique of Caprio's structure can be directly transferred to CMOS implementation as shown in Fig.1.2. Instead of employing current mirrors to provide current feedback as in the case of the transconductors proposed in [1.5] and [1.6], the cross-coupling transistors MN3—MN4 are utilized to *immediately* provide necessary compensating feedback current. If all the transistors are perfectly matched, it will render a linear transconductor with a transconductance  $g_m = 1/R_s$ . Alternatively, if a minimum supply voltage is required, PMOS transistors can be employed to complement NMOS devices in a place of either the input pair or the cross-coupling. It is worth noting that for a greater headroom and enhanced linearity, the constant bias current sources are not employed [1.8], the bias current is thus set by the degenerated resistor  $R_s$  and the DC common-mode input voltage level. This bias current is adaptively altered according to transconductance value ( $g_m$  is tuned by adjusting  $R_s$  which consists of resistive networks with triode MOS [1.8]), i.e., smaller  $g_m$  means smaller bias current compared to the fixed current consumption in a constant bias current source case. The non-linear cancellation technique of the circuit in Fig.1.2 is particularly attractive because it makes use of only two additional transistors, thus help reducing circuit complexity and minimising silicon area. Furthermore it does not require any extra bias current (unlike  $G_m$ 's in [1.5],

[1.6]) because the bias current of the cross-coupling transistors has been *reused* by the input transistor pair.

Fig.1.2 Current-feedback MOS transconductor with a cross-coupling for non-linearity compensation

The proposed transconductor in Fig.1.2 is designed in  $0.35\mu m$  CMOS technology to have a nominal single-unit  $g_m$  value of  $30\mu S$  (differentially) for an under-going analog baseband filter project. The aspect ratios W/L are  $50\mu m/0.35\mu m$  same for MN1-MN4. At a typical operating point, the transconductor consumes  $36\mu A$  under 3.0V supply with an input DC common-mode of 2.0V.

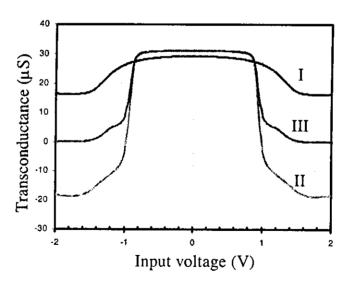

Fig.1.3 Transconductance curve of CF-G $_{\rm m}$  in Fig.1.2 (II) and Fig.1.4 compared with the conventional G $_{\rm m}$  (I) [1.8]

Simulations of the circuit have been performed via Spectre . For a comparative performance demonstration, simulations of the conventional source-degenerate transconductor [1.8] were also

carried out. The DC-sweep characteristic of the circuit in Fig.1.2 is illustrated as curve II in Fig.1.3. For an input range of  $\pm 0.8 \text{V}$ , the current-feedback  $G_m$  renders a flatter response compared to a conventional  $G_m$  (curve I) [1.8], hence better linearity. However, it can clearly be seen from curve II that this G<sub>m</sub> does inherit Caprio's quad's characteristics of limited voltage input range and inverted polarity of the transconductance. The input range is restricted because drains and gates of MN3 and MN4 are cross-connected making  $V_{\scriptscriptstyle DS}$  of these devices equipped with only one  $V_{\scriptscriptstyle GS}$  at zero-signal and consequently limit a signal swing head room. If  $V_m$  swing is too large, since MN1 and MN2 act as source followers, thus  $V_p$  of MN3 becomes very small and it would enter a triode operating region. Subsequently, current within MN3 and MN2 will be suddenly diminished and most of the output current will come out from MN1 and MN4, therefore the direction of output current (and transconductance) is inverted. This implies that in order to acquire a reasonably large input range, the cross-coupling transistors need to have large  $V_{as}$ . One way to achieve this is by connecting bulk to ground if a relatively large W/L ratio has to be maintained. In order to keep a supply voltage low, source and bulk of the input transistors MN1, MN2 should be joined together (thus not applicable to single-well CMOS processes). In such case, there is an unavoidable  $V_{\mathrm{sg}}$  mismatch between MN1 (MN2) and MN4 (MN3) and it inevitably degrades linearity of the transconductor because the nonlinear terms in (1.3) are not completely eliminated. Therefore the body effect has to be taken into account and the MOS V-I relationship is altered to [1.9]

$$I_D = \frac{\mu C_{ox}}{2\alpha} \frac{W}{L} (V_G - V_{THO} - \alpha V_S)^2$$

(1.4)

where  $V_{r,0}$  being the threshold voltage at zero source body voltage and the term  $\alpha$  represents a body effect, ideally  $\alpha=1$  for  $V_{sa}=0$ . The *inverted* polarity of the transconductance due to devices entering triode operating region may cause instability when employing such transconductor in high-level filters. This problem can be elevated by adding another transistor pair MN5-MN6 to MN3-MN4 and then cross coupling their drain currents to combine with those from MN1-MN2 to produce the total output current resulting in another transconductor structure as depicted in Fig.1.4. In this way, the drain voltages of MN5-MN6 will not be severely affected by the input voltage. Unlike MN3-MN4, they will not enter triode operating region by a large excursion of  $V_{in}$  and their drain currents are not polarity inverted. Such characteristic will thus be combined with the transconductance generated from MN1-MN4 and produce an overall *single*-polar transconductance (non-negative).

Fig.1.4 Single-polar current-feedback transconductor

The proposed  $G_m$  circuit of Fig.1.4 is designed with aspect ratios W/L of  $50\mu$ m/0.35 $\mu$ m same for MN1-MN6. At a typical operating point (nominal  $g_m$  =30 $\mu$ S), the transconductor consumes 38 $\mu$ A under 3.0V supply with an input DC common-mode of 2.0V. Transconductance plotted against DC-sweep input voltage is also shown as curve III in Fig.1.3 where it can be clearly seen that no polarity inversion has occurred. Comparing with the  $g_m$  obtained from the ordinary structure presented in [1.8], it is obvious that this proposed circuit of Fig.1.4 also renders a flatter  $g_m$  response which signifies better linearity — similar to the performance obtained from the  $G_m$  of Fig.1.2. Again, the input range is about  $\pm 0.8$ V, which is more than sufficient for the application currently being investigated.

#### 1.4 SIMULATION RESULTS

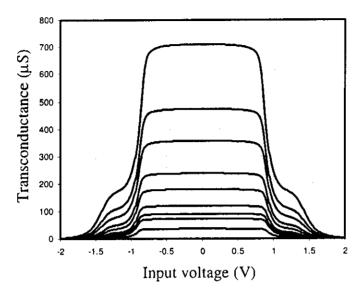

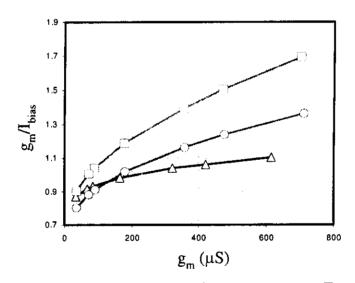

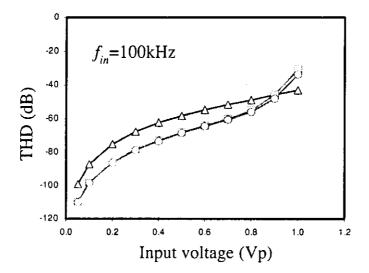

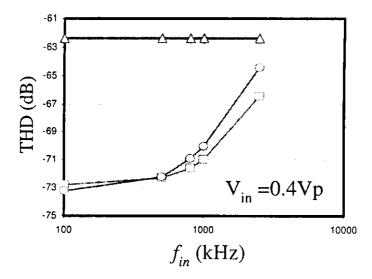

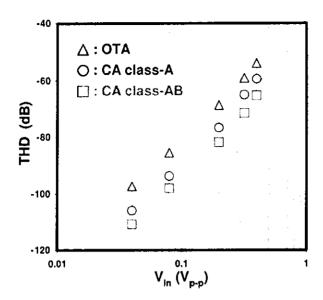

More simulations of the proposed transconductors have been carried out. Fig.1.5 shows the transconductance of the circuit in Fig.1.4 for different source degeneration resistor  $R_s$  values ranging from  $20\mathrm{k}\Omega$  (bottom) to  $1\mathrm{k}\Omega$  (top). The input range has been slightly shrunk to  $\pm 0.75\mathrm{V}$  for a small  $R_s$  =1k $\Omega$ . Furthermore current consumption for each transconductance value has been recorded and the transconductance/bias current efficiency is plotted in Fig.1.6. It is obvious that both proposed circuits of Fig.1.2 and Fig.1.4 render better  $g_m/I_{bias}$  efficiencies than those from the conventional  $G_m$  ([1.8]) for almost entire  $g_m$  range. Total harmonic distortions (THD) as a function of differential input amplitudes and frequencies are plotted in Fig. 1.7 and Fig.1.8 respectively for  $g_m$  =30 $\mu$ S. Evidently, the proposed transconductor renders a better THD performance by as much as 10dB over its the conventional  $G_m$  counterpart with an input amplitude up to 0.8V and with frequency range up to 1MHz.

Fig.1.5 The simulated transconductance for different values of the source-degenerated resistor

Fig.1.6 Transconductance/bias current efficiency:  $\Delta$  conventional  $G_m$  [8],  $\square$  Fig.1.2, O Fig.1.4

#### 1.5 CONCLUSION

A resistive source-degenerationCMOS transconductor with excellent linearity utilizing current-feedback has been described. The technique adds minimum complexity (just two or four additional transistors) to enhance linearity without extra current consumption, in other words high transconductance/current efficiency of an ordinary source degeneration transconductor is preserved

but with superior linearity performance. The transconductance's polarity inversion of Caprio's quad has also been solved by adding another cross-coupling transistor pair. The authors believe that it is possible to overcome  $V_{ss}$  mismatching problem by sizing the transistors with different W/L ratios similar to the technique presented in [1.6].

Fig.1.7 Simulated total harmonic distortion:  $\Delta$  conventional  $G_m$  [8],  $\Box$  Fig.1.2, O Fig.1.4

Fig.1.8 THD as a function of input frequency:  $\Delta$  conventional G<sub>m</sub> [8],  $\Box$  Fig.1.2, O Fig.1.4

#### REFERENCES

- [1,1] Z.Y. Chang, D. Haspeslagh and J. Verfaillie, "A Highly Linear CMOS Bandpass Filter with On-Chip Frequency Tuning," *IEEE Journal of Solid-State Circuits*, Vol. 32, No. 3, pp. 388-397, March 1997.

- [1.2] U. Chilakapati, T.S. Fiez and A. Eshraghi, "A CMOS Transconductor with 80-dB SFDR up to 10 MHz," *IEEE Journal of Solid-State Circuits*, Vol. 37, No. 3, pp. 365-370, March 2002.

- [1.3] A. Leuciuc and Y. Zhang, "A Highly Linear Low-Voltage MOS Transconductor," *Proc. IEEE Int. Symp. Circuits and Systems, Arizona 2002*, Vol. III, pp. 735-738.

- [1.4] R. Caprio, "Precision differential voltage-current converter," *IEE Electronics Letters*, Vol. 9, pp. 147-148, 1973.

- [1.5] W.-S. Chung and H.-W. Cha, "Bipolar linear transconductor," *IEE Electronics Letters*, Vol. 26, No. 10, pp. 619-621, 1990.

- [1.6] A. Worapishet and C. Naphaphan, "Current-feedback source degenerated CMOS transconductor with very high linearity," *IEE Electronics Letters*, Vol. 39, No. 1, pp. 17-18, 2003.

- [1.7] B. Gilbert, "Current-mode Circuits From A Translinear Viewpoint: A Tutorial" Chapter 2 in C. Tournazou et al (Eds) *Analogue IC Design: The Current-Mode Approach*, Peter Perigrinus Press, 1990.

- [1.8] F. Behbahani et al., "A Broad-Band Tunable CMOS Channel-Select Filter for a Low-IF Wireless Receiver," *IEEE Journal of Solid-State Circuits*, Vol. 35, No. 4, pp. 476-489, April 2000.

- [1.9] M. Ismail and T. Fiez, Analog VLSI: Signal and Information Processing, McGraw-Hill, 1994.

Khun Ying Long Athakravisunthorn Learning Resources Center Prince of Soughla University

**CHAPTER 2**

# A 1.8-V CMOS POLYPHASE FILTER FOR DUAL-MODE BLUETOOTH/ZIGBEE TRANSCEIVER

#### 2.1 INTRODUCTION

The low-intermediate frequency (low-IF) polyphase architecture has emerged as the preferred approach for achieving the required sensitivity in fully integrated wireless transceivers [2.1], [2.2]. Mainly driven by cost and power consumption, standard CMOS solutions for applications such as Bluetooth (IEEE 802.15.1) and ZigBee (IEEE 802.15.4) have set new challenges for circuit designers at both circuit and system levels. Bluetooth system has widely established itself in various well-known applications including wireless headsets, file sharing and printing, while ZigBee (also known as HomeRF Lite) is used for very simple wireless connectivity. The addition of ZigBee capability to a cell phone could enable the control of devices such as lights, electronic devices and central heating using the mobile handset. A dual-mode transceiver solution is being developed because in the price sensitive market for mobile devices, it is essential that this capability be added for minimal extra cost. Noting that coexistence issue of the two standards on the same frequency band is thoroughly discussed in IEEE Standard 802.15.4.

A polyphase filter or complex filter represents one of the key components in low-IF polyphase receiver. Owing to its asymmetric amplitude response, it has an ability to pass wanted channel signal while efficiently reject neighbouring channel interferers as well as unwanted image. A polyphase filter in this work is based upon transconductor-capacitor structure because of its simplicity, tuneability, linearity and high-frequency performance. The transconductor core circuit follows a linear, wide-tuning, low-noise and compact source degeneration type from [2.3] where the common-mode feedback and dc gain enhancement has employed a single network according to the topology originally proposed in [2.4].

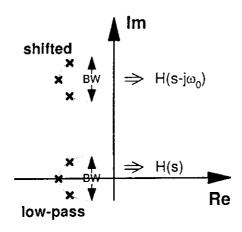

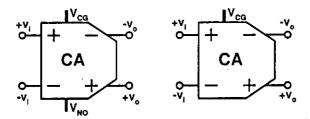

#### 2.2 REVIEW OF COMPLEX FILTERS

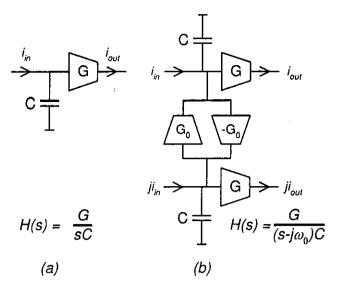

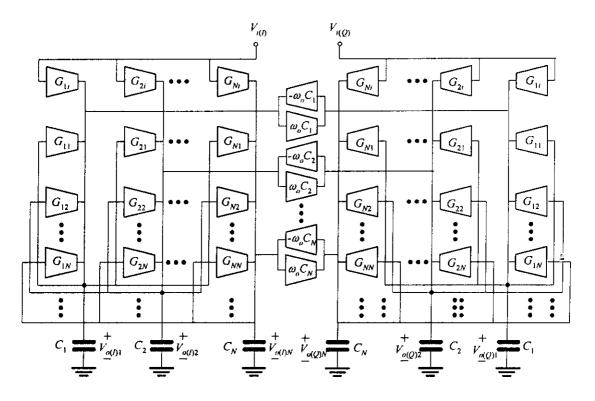

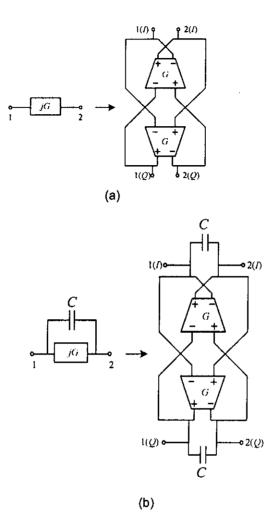

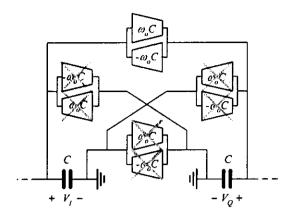

Fig.2.1 shows the basic principle of the complex filter. Starting with a real low-pass filter, the transformation  $s \to s - j\omega_0$  is applied. This shifts the poles up the imaginary axis by  $\omega_0$  and transforms the lowpass response into an equivalent bandpass response centred at  $\omega = \omega_0$ . The transformation preserves both amplitude and phase characteristics and produces the required feature of having no image response at negative frequency. Synthesis of complex filters follows similar procedures to those for real filters except that it makes use of complex integrators. Fig.2.2 shows transformation from real to complex integrators implemented in the  $G_m$ -C technique. The transfer characteristic of the complex integrator in Fig.2.2 (b) is described by,

$$H(s) = \frac{i_{out}(s)}{i_{in}(s)} = \frac{G}{(s - j\omega_0)C}$$

(2.1)

where  $\omega_0$  is frequency shift given by  $\omega_0=G_0/C$ . This demonstrates that the transformation  $s \rightarrow s - j\omega_0$  is being performed as required.

Fig.2.1: Complex filter basics

Fig.2.2: Current-mode  $G_m$ -C integrator (a) real (b) complex

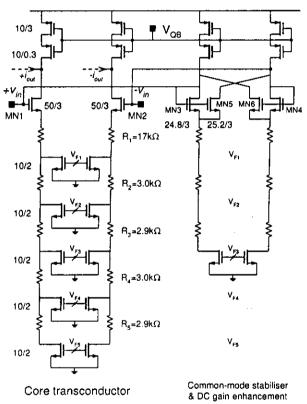

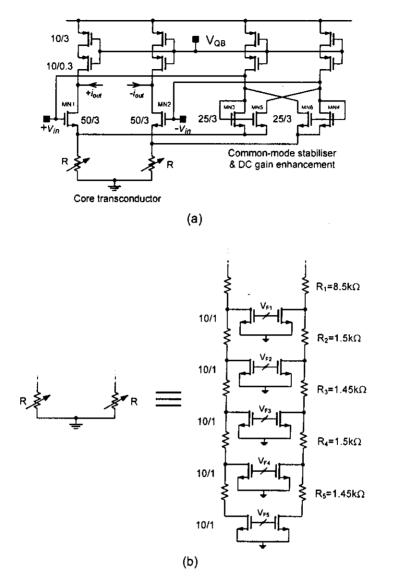

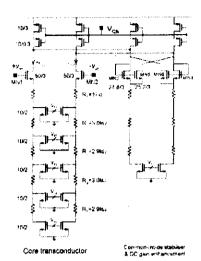

#### 2.3 TRANSCONDUCTOR CIRCUIT

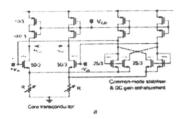

The variable wide-band resistor source-degeneration transconductor proposed in [2.3] possesses many advantages including good linearity, low-noise, high frequency capability and low supply voltage. However, such structure inherits a couple of weak points that need special attention. This type of transconductor structure is prone to common-mode instability when employed for filter realisation. It is thus necessary to deploy a common-mode feedback loop comprising common-mode voltage sensing and error amplifiers. Moreover a low dc gain of the transconductor necessitates an additional negative conductance network to provide sufficient dc gain in order to achieve a required filter's frequency response.

As depicted in Fig.2.3, instead of using two separate networks to enhance common-mode stability and dc gain, a single network (MN3-MN6) adopted from the topology presented in [2.4] is employed. Its main feature is to ensure common-mode stability where the network forms a low impedance load for common signals and a high impedance load from differential signals, effectively resulting in common-mode stability. The technique has been successfully demonstrated with G<sub>m</sub>C filters based on an inverter-type transconductor [2.5]-[2.9]. The second important feature is to help increase dc-gain of the transconductor. And this can be simply achieved by sizing transistors so that a positive feedback current from MN5-MN6 is higher than the negative feedback from MN3-MN4. Two-in-one

functionality thus allows additional devices to be kept at minimum; hence this helps save extra silicon area and power consumption.

The transconductor in Fig.2.3 possesses a nominal transconductance value of  $20\mu\text{S}$  (V<sub>F3</sub>=0.7V). Note that simple cascode PMOS current sources are employed to supply bias currents to the transconductor. The transconductor also deploys a tuning technique from [2.3]. Five tuning step are required in this case to ensure a transconductance continuous sweep of  $\pm 50\%$  from the nominal value; each tuning voltage can be varied between 0.6V and 1.8V to adjust degeneration NMOS triode resistance.

Fig.2.3: Transconductor with common-mode stabilizer and dc gain enhancement

At any time, only one pair of these degeneration NMOS's is on and the one-side degeneration resistance  $R_{di}$  is (only one  $V_{Fi}$  is on)

$$R_{di} \approx \mu_n C_{ox} \left(\frac{W}{L}\right)_i \left(V_{Fi} - V_{th}\right) + \sum_{\substack{n=1 \ \text{ladder resistance}}}^{i} R_n$$

$$\text{triode-MOS resistance}$$

(2.2)

where  $\mu_{\rm n}$ ,  $C_{\rm ox}$  and  $V_{\rm th}$  are conventional parameters for NMOS transistor and the differential transconductance is approximately equal to  $1/R_{\rm dr}$ . To ensure a continuous transconductance sweep, the ladder resistors have to be designed according to (2.2) so that the adjacent tuning steps have adequate transconductance overlapping at their tuning boundaries when  $V_{\rm FI}$  is switched from one step to another. Because of a limited maximum available tuning voltage of 1.8V, a wide triode resistance variation can be achieved by employing a low threshold voltage NMOS device ( $V_{\rm th}$ ~0.4V) available in the technology as a tuning triode-MOS resistor. However, it is typical to have large  $V_{\rm th}$  for the core transconductor MOS, MN1-MN2. This is because it normally happens that drain and gate voltages swings in opposite directions (sometimes with the same magnitude) from the same quiescent voltage (due to filter's cascade and feedback structure) and having a large  $V_{\rm th}$  device will help maintain the transistors in saturation for large signal swing. Note that some of the transistors and resistors within the common-mode stabiliser (drawn in the light shade) can be omitted to save chip area without severely disturbing the circuit operation. It has only been included in Fig.2.3 to imitate the core transconductor structure.

Compare this transconductor to the class-AB inverter-type MOS transconductor employed for a dual-mode polyphase filter in [2.7]-[2.9], the proposed transconductor is inherently insensitive to supply voltage variation and it operates in a class-A manner.

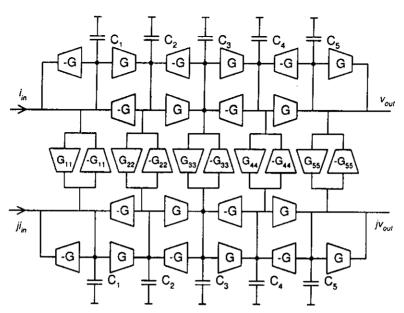

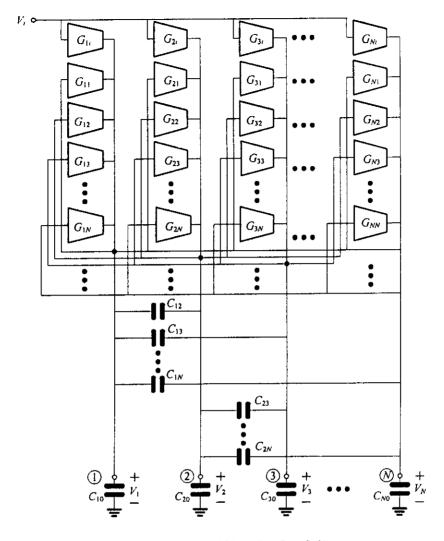

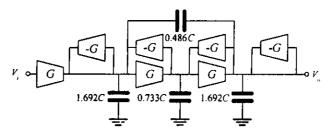

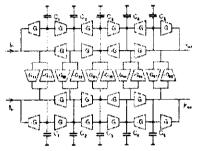

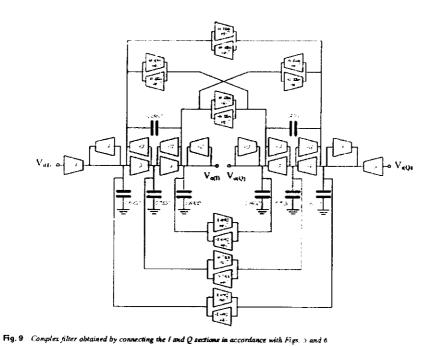

#### 2.4 FILTER DESIGN

A 5<sup>th</sup>-order 0.5dB equiripple Chebyshev complex filter depicted in Fig.2.4 is chosen for this work [2.7]-[2.9]. The design values for ZigBee and Bluetooth responses are given in Table 2.1. Notice that the design values are half of those used in [2.7]-[2.9] in order to minimise power consumption not higher than 2.5mW (this moderate power consumption has also been achieved by the 5<sup>th</sup>-order polyphase filter in [2.9]).

Fig.2.4: Channel filter architecture

Table 2. 1: Design values for dual-mode filter

| Parameters      | Bluetooth         | ZigBee            |

|-----------------|-------------------|-------------------|

| G               | 20 <i>µ</i> S     | 20 <i>µ</i> S     |

| G <sub>11</sub> | 56.86 <i>μ</i> S  | 56.86 <i>μ</i> S  |

| G <sub>22</sub> | 41.99 <i>µ</i> S  | 41.99 <i>µ</i> S  |

| G <sub>33</sub> | 84.70 <i>μ</i> \$ | 84.70 <i>µ</i> S  |

| G <sub>44</sub> | 40.99 <i>μ</i> S  | 40.99 <i>μ</i> \$ |

| G <sub>55</sub> | 56.86 <i>µ</i> S  | 56.86µS           |

| C <sub>1</sub>  | 9.05 <i>p</i> F   | 4.53 <i>p</i> F   |

| C <sub>2</sub>  | 6.53 <i>p</i> F   | 3.27pF            |

| C <sub>3</sub>  | 13.48 <i>p</i> F  | 6.74 <i>p</i> F   |

| C <sub>4</sub>  | 6.53 <i>p</i> F   | 3.27 <i>p</i> F   |

| C <sub>5</sub>  | 9.05 <i>p</i> F   | 4.53 <i>p</i> F   |

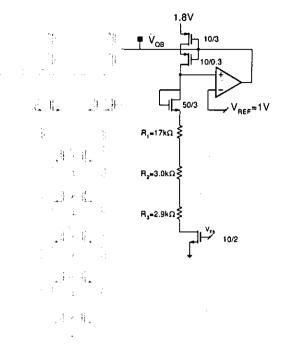

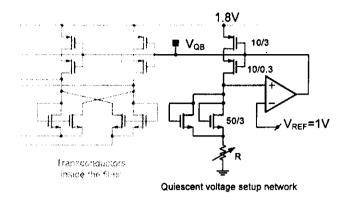

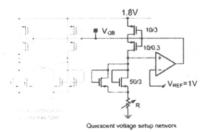

A single feedback loop circuit shown in Fig.2.5 sets quiescent voltage  $V_{QB}$  for all transconductors within the filter. The diode-connected MOS (W/L=50 $\mu$ m/3 $\mu$ m) emulates the fact that under a quiescent condition, transistors MN3, MN5 and MN4, MN6 within the common-mode reject network in Fig.2.3 resemble a diode-connected NMOS. In this design the quiescent voltage is set to be at 1V. It should be also noted that the op-amp employed in Fig.2.5 is not required to be high performance; hence it can be easily designed under 1.8-V supply.

<u>.</u>

Quiescent voltage setup network

Fig.2.5: Quiescent voltage setting-up circuitry

#### 2.5 SIMULATION RESULTS

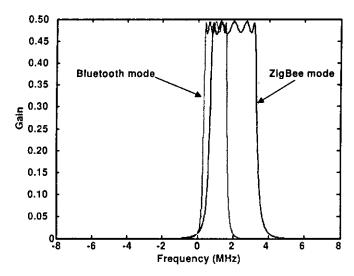

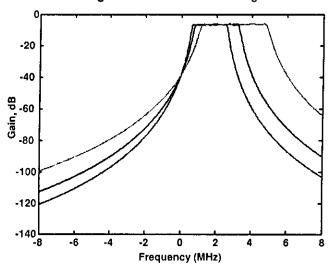

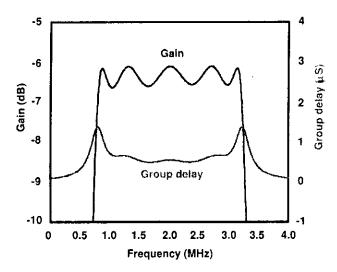

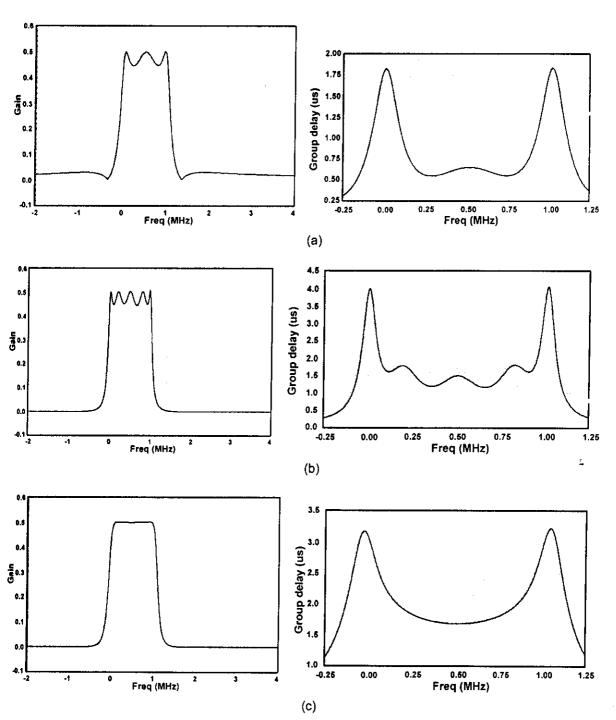

All the simulations have been carried out using Spectre with Cadence design suite. Simulated frequency response of the complex filter employing 3.3-V 0.18µm digital CMOS process is shown in Fig.2.6-Fig.2.8. It can be seen that the simulated responses are very close to ideal. Note that the actual capacitor values have been trimmed according to the method described in [2.8] to take parasitic capacitance into account. Fig.2.6 shows two modes of operation (Bluetooth and ZigBee), obtained by switching the values of capacitor with the common set of transconductors. Fig.2.7 illustrates frequency tuning at nominal and two extremes by adjusting tuning voltage. This center frequency tuning capability of > 80% is more than enough to encounter process and temperature variations.

Fig.2.6: Filter mode switching

Fig.2.7: Frequency tuning in ZigBee mode

Fig.2.8: ZigBee's passband response

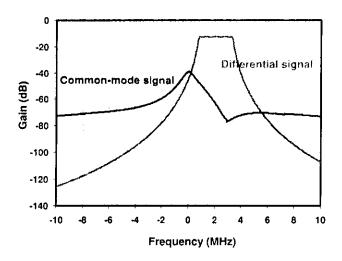

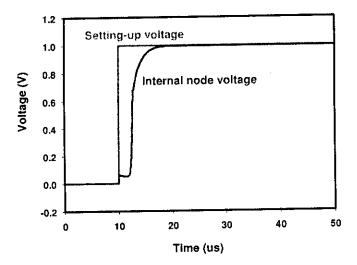

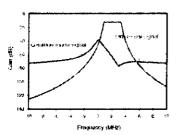

The filter common-mode rejection ability has been investigated by measuring common-mode signal frequency response and compare with differential signal as show in Fig.2.9. It can be seen that although the structure of Fig.2.3 does not reject common-mode signal *locally*, but globally the filter does have ability to suppress common-mode signals. The filter has also been subjected to a transient common-mode step response stability test [2.3], and the results guarantee its unconditional stability as illustrated in Fig.2.10.

Fig.2.9: Filter's frequency response: differential vs common-mode (single-end output)

Fig.2.10: Stability test with step response

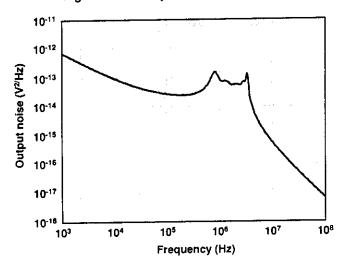

Fig.2.11: Noise response (ZigBee mode)

Fig.2.12: Third-order intermodulation

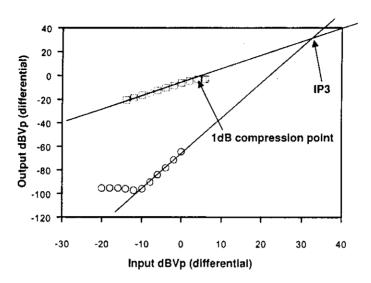

The ZigBee output differential noise is shown in Fig.2.11 where the total output noise integrated over the 100MHz bandwidth renders output noise power voltage of  $2.5 \times 10^{-7} \text{V}^2$ . The ZigBee signal compression characteristic of ZigBee-mode filter is shown in Fig.2.12 and it demonstrates a linear gain up to an input amplitude of 1Vp (0dBVp) differential and an input referred 1-dB compression point of 1.59Vp (or 4.03dBVp) differential (with corresponding output voltage of 0.68Vp). The signal-to-noise ratio is thus found to be 62.3dB.

The in-band spurious free dynamic range (SFDR), where the inter-modulation product has the same power as the filter noise, is found to be 51.3dB and 53.4dB for ZigBee and Bluetooth modes respectively. Out-of-band intermodulation of the distant blockers was also simulated as also shown in Fig.2.12 for ZigBee case (input tones at 6MHz and 10MHz for ZigBee and 3MHz and 5MHz for Bluetooth). It shows the ZigBee third-order intermodulation characteristic indicating an input referred third-order intercept point (IIP3) of 33dBVp differential with corresponding out-of-band SFDR of 59.6dB. The whole filter draws a total current of 1.38mA from a single 1.8-V supply. The overall performance for both modes is summarised in Table 2.2.

#### 2.6 CONCLUSION

A 1.8V CMOS dual-mode fifth-order polyphase G<sub>m</sub>C filter for Bluetooth/ZigBee transceiver has been designed. The complex bandpass filter is based on Gm-C filter structure with appropriate crossing transconductors to shift lowpass response to the required IF frequencies. It deploys a simple

source degeneration transconductor integrated with a network, which could simultaneously provide common-mode stability and dc gain enhancement.

Table 2.2: Summarised filer performance

| Filter Response        | Chebyshev                           |                                     |  |

|------------------------|-------------------------------------|-------------------------------------|--|

| Filter Order           | 5+5                                 |                                     |  |

| Filter ripple          | 0.5dB                               |                                     |  |

| Supply voltage         | 1.8V                                |                                     |  |

| Process                | 3.3V, 0.18 <i>µ</i> mCMOS           |                                     |  |

| Supply current         | 1.38mA                              |                                     |  |

| Mode                   | Bluetooth                           | ZigBee                              |  |

| Centre Frequency       | 1MHz                                | 2MHz                                |  |

| Bandwidth              | 1.2MHz                              | 2.4MHz                              |  |

| Gain                   | -6.18dB                             | -6.18dB                             |  |

| Output noise           | 1.4×10 <sup>-7</sup> V <sup>2</sup> | 2.5×10 <sup>-7</sup> V <sup>2</sup> |  |

| Input 1dB Comp.        | 1.59Vp                              | 1.59Vp                              |  |

| Signal/Noise (SNR)     | 64.9dB                              | 62.3dB                              |  |

| IIP3 (distant blocker) | 36.4dBVp                            | 33dBVp                              |  |

| SFDR                   |                                     |                                     |  |

| (a) Distant blocker    | 62.1dB                              | 59.6dB                              |  |

| (b) In-band            | 53.4dB                              | 51.3dB                              |  |

#### REFERENCES

- [2.1] J. Crols and M. J. Steyaert, "Low-IF Topologies for High-Performance Analog Front Ends of Fully Integrated Receivers," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, vol. 45, pp. 269-282, March 1998.

- [2.2] B. J. Minnis, P. A. Moore, A. W. Payne, and N. P. J. Greer, "A low-IF polyphase receiver for DECT," IEEE International Symposium on *Circuits and Systems*, 2000.

- [2.3] F. Behbahani, W. Tan, A. Karimi-Sanjaani, A. Roithmeier, and A. A. Abidi, "A Broad-Band Tunable CMOS Channel-Select Filter for a Low-IF Wireless Receiver," *IEEE Journal of Solid-State Circuits*, vol. 35, pp. 476-489, April 2000.

- [2.4] B. Nauta and E. Seevinck, "Linear CMOS transconductance element for VHF filters," *Electronics Letters*, vol. 25, pp. 448-450, March 1989.

- [2.5] B. Nauta, "A CMOS transconductance-C filter technique for very high frequencies," *IEEE Journal of Solid-State Circuits*, vol. 27, pp. 142-153, Feb. 1992.

- [2.6] P. Andreani and S. Mattison, "On the Use of Nauta's Transconductor in Low-Frequency CMOS  $g_m$ -C Bandpass Filters," *IEEE Journal of Solid-State Circuits*, vol. 37, pp. 114-124, Feb. 2002.

- [2.7] J.B. Hughes, A. Spencer, A. Worapishet, and R. Sitdhikorn, "1mW CMOS polyphase channel filter for Bluetooth," IEE Proc-Circuits Devices Syst., Vol. 149, No. 516, October/December, 2002, pp.348-354.

- [2.8] J.B. Hughes, A. Spencer, A. Worapishet, and R. Sitdhikorn, "A low-power, low-voltage Bluetooth channel filter using class AB CMOS transconductors", chapter 5 in *Wireless Communication Circuits and Systems*, edited by Y. Sun, (IEE, Stevenage, UK, 2004).

- [2.9] B. Guthrie, T. Sayers, A. Spencer, and J. Hughes, "A CMOS Gyrator Low-IF for a Dual-Mode Bluetooth/ZigBee Transceiver," Proceedings of Custom Integrated Circuit Conference, 2004.

- [2.10] P. Choi et al., "An Experimental Coin-Sized Radio for Extremely Low-Power WPAN (IEEE 802.15.4) Application at 2.4 GHz," *IEEE Journal of Solid-State Circuits*, vol. 38, pp. 2258-2268, December 2003.

# APPLICATION OF REVERSE-ACTIVE *NPN*S FOR COMPACT, WIDE-TUNING $F_T$ -INTEGRATION-BASED FILTERS IN SIGE HBT BICMOS TECHNOLOGY

#### 3.1. Introduction

The rapid growth of today's wireless multi-gigabit communication market has placed an ever increasing demand on integrated filter performance particularly in terms of very high operating frequencies with acceptable dynamic range and low power consumption. Among conventional active filtering techniques such as  $G_m$ —C and log—domain filters,  $f_T$ —integration technique has portrayed itself as a viable alternative for very high frequency applications [3.1]-[3.4].

A mature SiGe HBT BiCMOS technology is an excellent match for realisation of cost-effective, highly integrated high-speed data communication and wide-bandwidth digital wireless architectures at microwave frequencies. This is because high performance analog circuitry (provided by heterojunction bipolar transistor —HBT) can co-exist with sophisticated digital blocks (CMOS). Bandgap engineering enables process designers to achieve a SiGe HBT with all-around superior performances compared to a conventional Si BJT device [3.5]-[3.8].

This work demonstrates the feasibility in applying HBT devices in SiGe BiCMOS technology to  $f_T$ —integration technique. Specifically, the HBT's will be employed to implement a low-voltage, wide-tuning 5-GHz  $f_T$ —integration-based bandpass filter. It will be shown that a large frequency tuning range at microwave operating frequencies is accomplished in the SiGe filter via the existing structure using lateral pnp's as large base transit time tuning devices. The improved structure using reversed active vertical npn's with a significant reduction in chip area is proposed.

### 3.2. $f_{\tau}$ -Integration Principle

$f_T$ —integration technique has been thoroughly discussed in previous literatures [3.1]-[3.4] and only a brief overview of the principle is addressed here for better circuit understanding in subsequent sections.

Base charging dynamic of a bipolar junction transistor results in a charge control equation which relates large-signal base current  $l_b$  and collector current  $l_c$  as

$$I_b = \tau_b \frac{dI_c}{dt} + \frac{I_c}{\beta_0}$$

(3.1)

where  $\mathcal{T}_b$  is the transit time in the base. This mathematical function of integration lies as a basis of  $f_T$ —integration. The operation of SiGe heterojunction bipolar junction transistor (HBT) is also governed by the base charging dynamic similar to the conventional homojunction BJT. Therefore it is conceptually feasible to apply  $f_T$ —integration technique to HBT's for filter implementation.

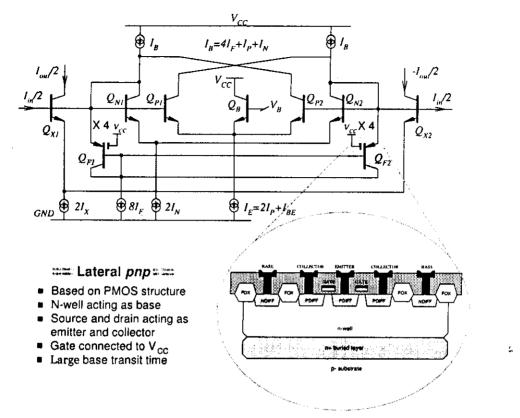

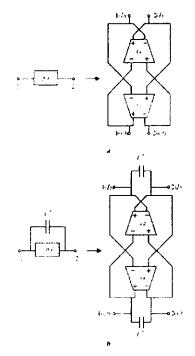

## 3.3. WIDE-TUNING $f_{\tau}$ -Integrator Design in SiGe HBT BiCMOS Technology

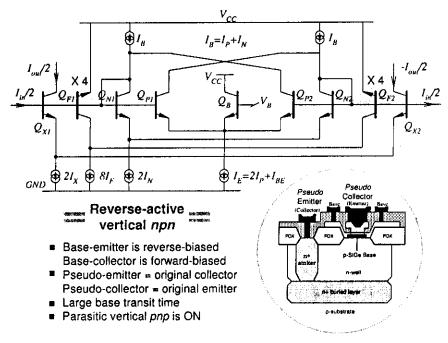

Based upon the  $f_T$ —integration principle presented in the previous section, the first version of the  $f_T$ —integrator designed within SiGe HBT 0.8 $\mu$ m BiCMOS process is shown in Fig.3.1 which has been migrated from the low-voltage  $f_T$ —integrator presented in [3.4]. Four lateral pnp's  $Q_F$  connected in parallel have been used on each side of the integrator in order to achieve the required nominal operating frequency of 5GHz and wide frequency tuning range. Note that the lateral pnp symbol has an extra node indicating a gate terminal which always has to tied to the most positive supply. This is because this lateral pnp is simply constructed from the existing PMOS structure, its gate thus has to be biased positively so that channel inversion never occurs.

Fig.3.1:  $f_r$ -integrator in SiGe BiCMOS with lateral pnp as tuning device (migrated from[3.4])

The unity-gain frequency  $f_U$  of the  $f_T$ —integrator presented in Fig.3.1 can be expressed as

$$f_{U} = \frac{1}{2\pi\tau_{b} \left\{ 1 + m \frac{\tau_{bf}}{\tau_{b}} \frac{I_{F}}{I_{X}} + \frac{I_{P}}{I_{X}} + \frac{I_{N}}{I_{X}} \right\}}$$

(3.2)

where  $\mathcal{T}_b$  is the base transit time of the forward-active npn and  $\mathcal{T}_{bl}$  is that of the frequency-tuning device  $Q_F$  with m being the number of  $Q_F$  in parallel. Since typical values for  $I_P$  and  $I_N$  are negligibly small compared to  $I_X$  and  $I_F$ , the tuning range can be estimated from (3.2) to be

$$\frac{f_{U_{\text{max}}}}{f_{U_{\text{spin}}}} \approx \frac{f_{U}|_{\mathfrak{G}I_{F}=0}}{f_{U}|_{\mathfrak{G}I_{F}=I_{X}}} = 1 + m \frac{\tau_{bf}}{\tau_{b}} \frac{I_{F,\text{max}}}{I_{X}} = 1 + m \frac{\tau_{bf}}{\tau_{b}} \frac{p \cdot I_{F0}}{I_{X}}$$

$$(3.3)$$

where m=4 in Fig.3.1.  $I_{Fmax}$  is the maximum possible frequency-tuning current which may be written as  $I_{Fmax} = p \cdot I_{F0}$ , where p is the ratio of the maximum possible  $I_F$  relative to the nominal bias value  $I_{F0}$ . Normally the ratio p is the same for any type of HBT or BJT. Equation (3.3) suggests that the term on the right hand side has to be large in order to achieve a wide tuning range. An advantage in utilizing

lateral pnp, commonly available in standard BiCMOS process, for  $Q_F$  is a considerable tuning range improvement while keeping power consumption at minimum. That is, only a small m is required to accomplish a large tuning range, owing to the pnp 's inherently large base transit time. Moreover, the lateral pnp normally requires low bias current  $I_{F0}$ . In other words, with lateral pnp, the second term in (3.3) can be made large without sacrificing excessive extra current consumption. Small nominal bias current also helps minimise collector and base shot noise.

Fig.3.2: The proposed f<sub>r</sub>-integrator with vertical reverse-active npn as frequency tuning device

However, the employment of lateral pnp results in one major disadvantage of occupying huge silicon area and so this might not be an ultimate solution for tuning range extension. It would be ideal if there is a more compact device but with an inherently large base transit time and low nominal bias current in a similar order to that of the lateral pnp. Our proposal is to employ a vertical npn operating in a reverse-active region, i.e., with the reverse biased base-emitter and forward biased base-collector junctions. Because of its asymmetry (both in doping profile and physical structure, see Fig.3.2), a reverse-active npn possesses an inferior characteristic compared to the forward-active mode. The large base transit time of a reverse-active npn, which is normally considered inferior, can be turned into an advantage by performing a significant role of frequency tuning range enhancement. In a typical BICMOS, bipolar or SiGe BICMOS process including the one employed in this work, it is found that lateral pnp and reverse-active npn possess a similar large value of  $\mathcal{T}_{br}$ , which means that these two

types of devices require the same number of transistors to obtain the same tuning range. Therefore with a benefit of saving chip area, there is no penalty on either current consumption or number of devices in replacing lateral pnp with a reverse-active vertical npn. In this way, we are able to extend  $f_T$ —integrator's frequency tuning range without sacrificing neither power consumption nor chip area by simply utilising npn operation in a region which has been widely regarded worthless.

The  $f_T$ —integrator structure employing a reverse-active vertical npn as frequency-tuning device is illustrated in Fig.3.2. Similar to the lateral pnp case, four reverse-active npn are employed on each side of the integrator in order to achieve a 5GHz nominal operating frequency. Both circuits in Fig.3.1 and Fig.3.2 use a supply voltage of  $V_{BE}$  +  $2V_D$ , where  $V_D$  is the voltage drop across each current source and the typical supply voltage could be estimated to be 0.8 + 2(0.5) = 1.8V.

There are various issues that have to be taken care of when designing circuit using reverse-active vertical npn. Firstly, voltage across emitter-base junction has to be kept lower than a relatively low emitter-base breakdown voltage. The supply voltage of circuit in Fig.3.2 is thus restricted to a low value. If it is necessary to have a high supply voltage (e.g. 3V), the reverse-active  $npn\ Q_p$  in Fig.3.2 can be modified by disconnecting its emitter (pseudo collector) from  $V_{CC}$  and tying this to the base. In this way, the  $Q_p$ 's has formed a diode-connected configuration and base-emitter breakdown damage can be avoided. Secondly, when operating the transistor in a reverse mode, the parasitic vertical pnp formed by base-collector-substrate structure is inevitably turned ON. Consequently, there will always be a small leakage current wasted into substrate.

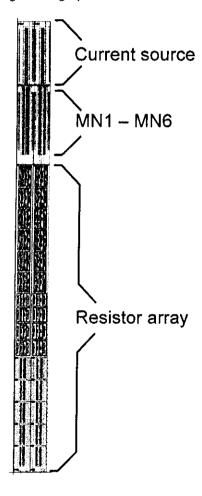

#### 3.4. SIMULATION RESULTS

The resonators based on the proposed integrators of Fig.3.1 and Fig.3.2 have been simulated with  $V_{cc}$ =1.8V using SpectreRF within Cadence design platform. The devices are taken directly from the library of the foundry's design kits of HBT SiGe 0.8µm BiCMOS process without any modification. A double-base npn occupies a total area of  $60\mu m^2$  (effective emitter area =  $2\mu m \times 0.8\mu m$ ) which is much smaller than  $400\mu m^2$  of lateral pnp (effective emitter area =  $3.6\mu m \times 3.6\mu m$ ). Therefore, in this particular technology, the reverse-active vertical npn occupies silicon area less than one-sixth of the lateral pnp's area which significantly help optimise circuit compactness and reduce fabrication cost. For rough estimation, if a single vertical npn represents one unit chip area, it would mean that the proposed integrator of Fig.3.2 consumes only one-fourth of the area occupied by the integrator in Fig.3.1. Regarding device characteristics, the npn HBT has a peak  $f_T$  of 30GHz at bias collector

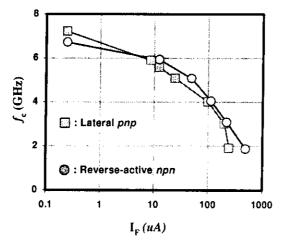

current = 750 $\mu$ A with corresponding  $\beta_0$  of 80 and base resistance = 300 $\Omega$ . In a reverse-active mode, the same device possesses a peak  $f_T$ = 800MHz with  $\beta_0$  = 10 at collector current of 80 $\mu$ A. Comparing to a reverse-active npn, lateral pnp have a slightly superior device characteristic with peak  $f_T$  =3GHz at collector current of 90 $\mu$ A with the corresponding  $\beta_0$  =20.

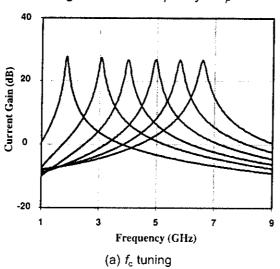

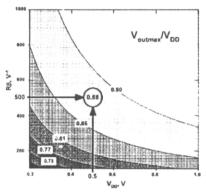

Simulation results show that the centre frequency ( $f_c$ ) can be widely tuned from 1.9GHz to 6.7GHz by varying  $I_F$  from 600 $\mu$ A to 0.25 $\mu$ A while fixing  $I_X$  at 750 $\mu$ A as shown in Fig.3.3. Such a wide frequency tuning of over 300% is a solid confirmation of reverse-active npn and lateral pnp's expected functionalities. Resonator frequency responses are illustrated in Fig.3.4 indicating centre-frequency ( $f_c$ ) and quality factor (Q) tuning.

Fig.3.3: Centre-frequency vs I,

Fig.3.4: Frequency response (reverse-active)

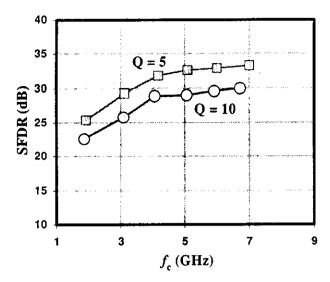

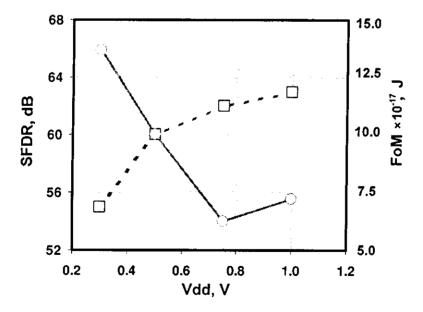

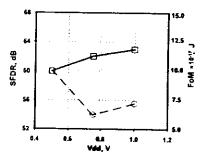

The spurious-free dynamic range, SFDR (ratio between a wanted signal and an unwanted third-order intermodulation at the point where the third-order intermodulation power is equal to noise power) is plotted against centre frequencies is shown in Fig.3.5 for two values of Q = 5 and 10. Note that SFDR is simulated with input two-tone signals of 0.5% frequency separation and the noise power is measured by integrating ac-simulated noise within -3dB signal bandwidth. At nominal centre frequency of 5GHz, the SFDR's are found to be 30dB and 33dB for Q = 10 and 5 respectively.

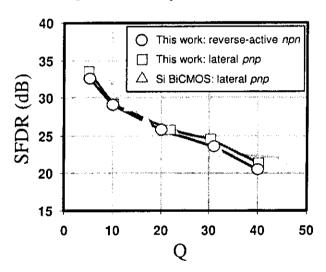

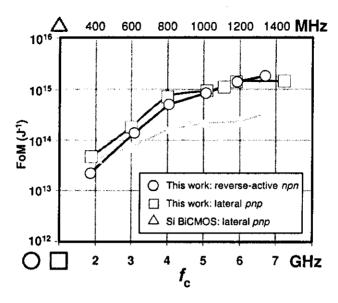

Fig.3.6 illustrates how SFDR varies with Q for the proposed circuits at  $f_c$ =5GHz and they are compared with the prototype in Si BiCMOS at  $f_c$  =1GHz. It can be seen that the proposed SiGe circuits render SFDR similar to those reported in [3.4] but with an operating frequency higher by fivefold. A fair comparison of filter overall performance is normally obtained by means of a figure of merit (FoM) which is defined here as

$$FoM = \frac{f_c \times SFDR}{Power consumption per pole}$$

(3.4)

According to FoM definition, the filter with a better performance possesses a higher FoM. FoM comparisons are plotted against  $f_c$  in Fig.3.7 for Q = 10. It is clear that at the region around nominal operating frequencies, the proposed circuits (both with lateral pnp and reverse-active npn as a tuning device) give better FoM over the filter implemented in Si BiCMOS where an improvement by a factor as large as four can be observed.

Fig.3.5: SFDR vs  $f_c$  (reverse-active)

Fig.3.6: SFDR vs Q (reverse-active)

Fig.3.7: Figure of merit comparison

#### 3.5. Conclusion

$f_{\rm T}$ —integration technique has been successfully demonstrated via simulations in HBT SiGe 0.8µm BiCMOS technology. Addition to existing technique in deployment of a lateral pnp for frequency tuning range enhancement, a reverse-active vertical npn has been proposed to achieve the same task while also keeping current consumption and chip area at minimum. The resonators can be widely tuned from about 2GHz to more than 6GHz, i.e., tuning range is greater than three-fold. At nominal, the resonators render SFDR of 30dB and 33dB for Q = 10 and 5, respectively. FoM comparison between the SiGe filters and the previous prototype implemented in Si enjoys improved performances as large as four times.

#### REFERENCES

[3.1] J. Mahattanakul, C. Toumazou and S. Pookaiyaudom, "Low-distortion Current-mode Companding Integrator Operating at  $f_T$  of BJT," *Electronics Letters*, Vol. 32, No. 21, October 1996.

[3.2] A. Worapishet and C. Toumazou, "f<sub>T</sub> Integrator — A New Class of Tuneable Low-Distortion Instantaneous Companding Integrators of Very High-Frequency Applications," *IEEE Transactions on Circuits and Systems - II: Analog and Digital Signal Processing*, Vol. 45, No. 9, pp. 1212-1219, September 1998.

- [3.3] P. Khumsat, A. Worapishet, and A.J. Payne, "f<sub>T</sub> integration employing lateral *pnp*'s in BiCMOS/CMOS technologies," *Electronics Letters*, Vol. 35, No. 24, pp. 2138-2140, November 1999.

- [3.4] P. Khumsat, A. Worapishet, and A.J. Payne, "Wide-tuning, low-voltage 1GHz bandpass filter based on  $f_{\Box}$  integration," in Proceedings of the 45th IEEE Midwest Symposium on Circuits and Systems, August 2002.

- [3.5] M. Feng, S.C. Shen, D.C. Caruth, and J.J. Hunag, "Device Technologies for RF Front-End Circuits in Next-Generation Wireless Communications," *Proceedings of the IEEE*, Vol. 92, No. 2, Feb. 2004.

- [3.6] K. Washio, "SiGe HBT and BiCMOS Technologies for Optical Transmission and Wireless Communication Systems," *IEEE Transactions on Electron Devices*, Vol. 50, No. 3, March 2003.

- [3.7] J.D. Cressler, "SiGe HBT Technology: A New Contender for Si-Based RF and Microwave Circuit Applications," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 46, No. 5, May 1998.

- [3.8] M. Soyuer, H.A. Ainspan, M. Meghelli, and J.-O. Plouchart, "Low-Power Multi-GHz and Multi-Gb/s SiGe BiCMOS Circuits," *Proceedings of the IEEE*, Vol. 88, No. 10, October 2000.

## HIGH-GAIN CURRENT AMPLIFIERS FOR LOW-POWER MOSFET-C

**FILTERS**

#### 4.1 INTRODUCTION

The rapid growth of today's wireless communication market has placed an ever-increasing demand on integrated filter performance particularly in terms of linearity, dynamic range and low power consumption under a low voltage supply constraint. The MOSFET-C filter design technique has portrayed itself as a simple and effective method for integrating high complexity continuous-time filters on a single CMOS chip with large dynamic range and accurate frequency response [4.1]-[4.5].

A key building block in MOSFET-C filters (and also as in a classical active-RC filter) is an operational amplifier (OA). However, it has been demonstrated in [4.1], [4.2] that an operational transconductance amplifier (OTA) — typically consumes less power than OA, with sufficiently large transconductance, can also be employed as an active building block. Achieving a large transconductance OTA under a low voltage supply might not be straightforward. In the past decade, OTA have been extensively researched for various circuit applications [4.3]-[4.8]. This work employs a very high-gain current amplifier (CA) as an alternative to OA and OTA in MOSFET-C filter (active-RC) while still maintains a required filter realization. Previously, high-gain current amplifiers have also been used in voltage amplifier design ([4.9], [4.10], [4.11]) and recently in  $g_m$ C-Opamp high frequency filters ([4.12]) in order to give high-bandwidth and low-distortion performance.

#### 4.2 MOSFET-C Integrator Employing Current Amplifier

Consider a MOSFET-C or active-RC integrator employing an ideal current amplifier (CA) with current gain of  $A_i$  as an active building block in Fig.4.1, a simple analysis yield voltage output/input relationship (in terms of admittance Y and  $A_i$ )

$$\frac{v_{out}}{v_{in}} = -\frac{Y_1}{Y_2 + \frac{Y_2 + Y_L}{A_i}} \tag{4.1}$$

where  $Y_1=1/R$ ,  $Y_2=sC$  and  $Y_L$  = load admittance. If  $A_1 >> Y_2 + Y_L$ , an ideal integrator transfer function can be realised accordingly, that is

$$\frac{v_{out}}{v_{in}} = -\frac{Y_1}{Y_2} = -\frac{1}{sRC}$$

$$V_{in}$$

Fig.4.1 MOSFET-C or active-RC integrators employing high-gain current amplifiers

Similar to OA-RC and OTA-RC cases, because the current amplifier in Fig.4.1 is connected in a closed loop formation, therefore the current amplifier may be non-linear as long as high current gain is present, and no linearisation circuit is needed. Fig.4.2 shows a possible architecture of a very high-gain current amplifier. The high current gain of this current amplifier comes from an intermediate high-impedance node X and it is equals to  $A_i = Z_x \cdot G_m$ .

Fig.4.2 High-gain current amplifier concept

<u>.</u>

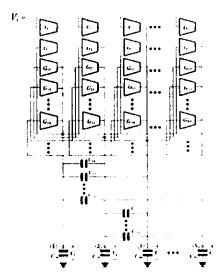

# 4.3 PROPOSED HIGH-GAIN CURRENT AMPLIFIERS FOR MOSFET-C OR ACTIVE-RC FILTERS

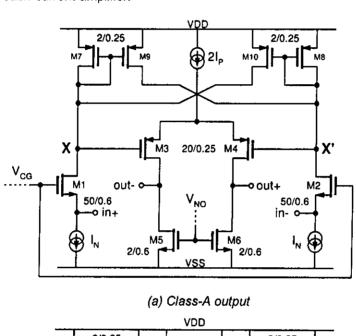

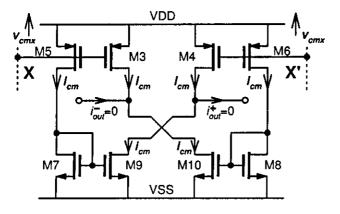

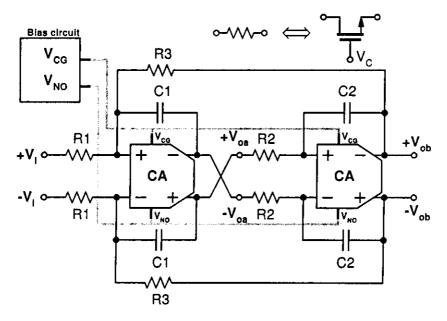

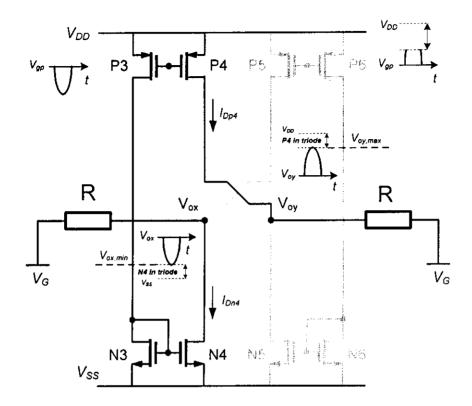

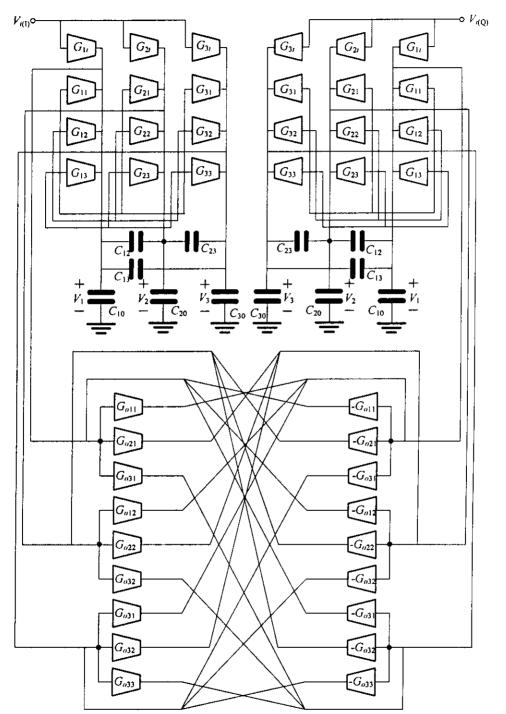

A balanced MOSFET-C integrator employing a high-gain current amplifier based upon the structure in Fig.4.2 is depicted in Fig.4.3a and Fig.4.3b. A common-gate NMOS structure M1-M2 is utilised as a current buffer allowing input current to flow into high impedance nodes X, X'. At these nodes in Fig.4.3a, a diode-connected PMOS (negative feedback, M7-M8) is combined with the cross-coupling PMOS (positive feedback, M9-M10) to realise high impedance. However, such high impedance is only recognised by differential signals. In contrast, these same nodes are seen by common-mode signals as low impedance, hence DC bias voltage can be established without requiring additional common-mode feedback (CMFB) amplifier as in case of the amplifier in [4.9]. This gain enhancement and DC voltage setting-up technique thus consumes no extra current consumption. An output stage of the amplifier utilises a PMOS source-coupled pair with current source 2I<sub>P</sub> where it provides capability of common-mode rejection for the amplifier. However, such structure resembles class-A output configuration, therefore the output current swing is limited by a current source (2I<sub>P</sub>).

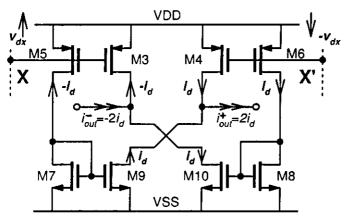

A more attractive current amplifier structure is shown in Fig.4.3b where PMOS M3, M4 are connected in parallel to M11, M13 and M12, M14 respectively in order to provide output current in a class-AB manner allowing large current signal excursion because it is not limited by fixed current source. This circuit thus should render better linearity than its counterpart in Fig.4.3a. However, this output structure requires M5-M6 and current mirrors M7-M10 with an appropriate cross-coupling to provide (i) common-mode rejection (ii) differential signal addition (combining drain signal currents of M5 with M4 and M6 with M3). Fig.4.4 illustrates how this particular output stage handle signals differently. Such circuit arrangement provides feed-forward common-mode rejection, but in a different manner to that proposed in [4.13], because the differential signals (and transconductances) of M3, M6 and M4, M5 are added constructively. Therefore it can effectively provide common-mode rejecting without incurring any penalty in the overall transconductance/bias-current efficiency, i.e., bias current consumed by M5-M8 is not wasted just for common-mode rejection.

Additional simple tuneable positive or negative resistance networks shown in Fig.4.5 could be attached to node X, X' of the circuits in Fig.4.3 so that the gain can be electronically adjusted. Note also that the amplifier bias setting voltages  $V_{CG}$  and  $V_{NO}$  are supplied from bias circuitries as described in the next section.

#### 4.4 SECOND-ORDER FILTER AND BIASING TECHNIQUE

Amplifiers of Fig.4.3 are employed to demonstrate applications in a high-order filter design, here a resonator as shown in Fig.4.6 whose structure is widely known [4.1], [4.2]. The resonator employs a bias network that sets all necessary DC voltages for the whole filter without requiring any additional CMFB amplifiers for each current amplifier.

2/0.25 2/0.25 M11 M13 M14 M12 2/0.25 2/0.25 X МЗ X'  $V_{CG}$ outout+ M1 М2 50/0.6 50/0.6 in+ 2/0.6 2/0.6 vss

(b) Class-AB output

(c) Symbolic representations

Fig.4.3 Proposed high-gain current amplifiers

(a) Common-mode: rejection

(b) Differential: addition

Fig.4.4 Signal handling of the output stage in Fig.4.3b

<u>\*</u>

Fig.4.5 Tuneable negative and positive resistance network

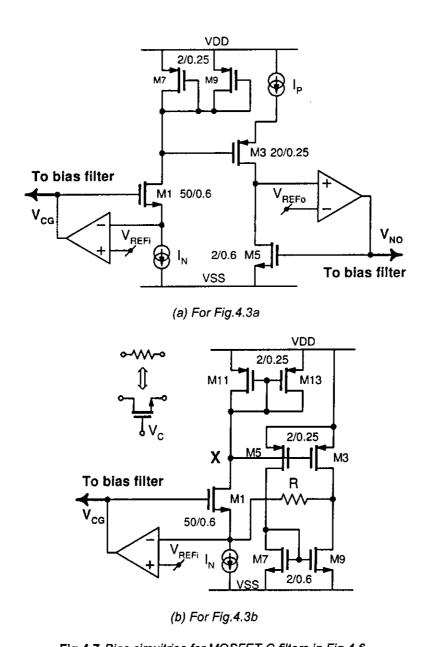

Such bias set-up network (Fig.4.7) employs a feedback servo loop to set  $V_{CG}$  for every current amplifier so that the DC voltage at amplifier's input terminals (sources of MN1 and MN2 in Fig.4.3) is equal to  $V_{REFi}=V_{SET}$ . In the filter structure with cascade configuration, it is common to bias amplifiers' input and output terminals at the same DC level to allow optimal signal swing. Therefore, the DC output voltage of each current amplifier should also be set at  $V_{SET}$ .

In most cases of MOSFET-C or active-RC filters (cascade configuration) [4.1]-[4.5], there are always interconnections between amplifiers' output and input terminals via resistors (or triode-MOS), and if these resistors carry infinitesimal DC currents, the DC output terminal voltages of the amplifiers will be automatically equal to those of input terminals. The second servo loop in Fig.4.7a with  $V_{REFo}=V_{SET}$  is thus needed to make sure that those interconnecting resistors carry no DC currents, where it sets voltage  $V_{NO}$  for every single current amplifier in the filter to make sure that M3 and M5 (M4 and M6) carry the same DC bias current. The bias network for the amplifier in Fig.4.3b (Fig.4.7b) does not require a second servo-loop because the output bias current of M3 and M4 is equal to M9 and M10 thanks to a common-mode rejection network as described in the previous section. Therefore the output bias voltage is set via resistor R and it equals  $V_{REFi}=V_{SET}$ .

Therefore in a high-order filter design, only *one* of this bias network is needed for the whole filters and it thus helps minimise power consumption and silicon area since no extra CMFB amplifiers are required for DC voltage setting up. The proposed current amplifiers in Fig.4.3 can be readily modified into two-stage OTAs by injecting input voltage signal at gates of M1, M2 with their sources joined together. However, each OTA necessitates high-performance CMFB amplifier at its output to set

up DC bias voltage and maintain filter stability. Such OTAs are thus not suitable for low-power filter design.

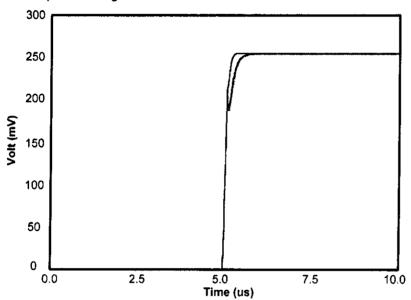

#### 4.5 SIMULATION RESULTS

The resonator of Fig.4.6 was simulated under 1-V supply voltage with  $V_{\text{SET}}$ =0.5V employing 0.18 $\mu$ m CMOS process. Using low threshold-voltage MOS ( $|V_{\text{TN}}|$  = 0.25V,  $|V_{\text{TP}}|$  = 0.25V)

Fig.4.6 MOSFET-C filter employing the proposed amplifiers.

1

Fig.4.7 Bias circuitries for MOSFET-C filters in Fig.4.6.

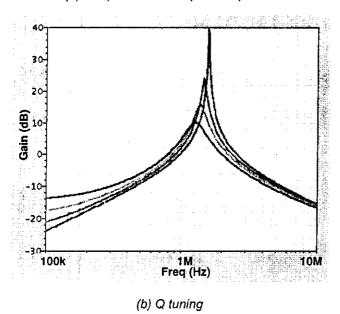

available in the process, the proposed current amplifier was employed and compared with a conventional balanced folded-cascode OTA ([4.6]). Note that the negative resistance network in Fig.4.5 is also attached at intermediate low-impedance node of such OTA to allow gain enhancement and Q control. Transistor sizes and bias currents between the proposed CAs and the OTA were selected such that these amplifiers consume same bias current and silicon area so that a fair comparison is recognised. However, in the case of the OTA, CMFB amplifiers were employed to set

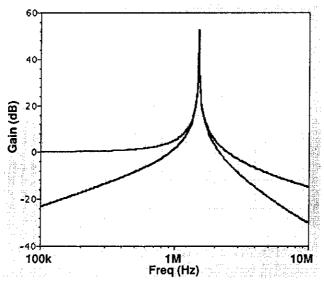

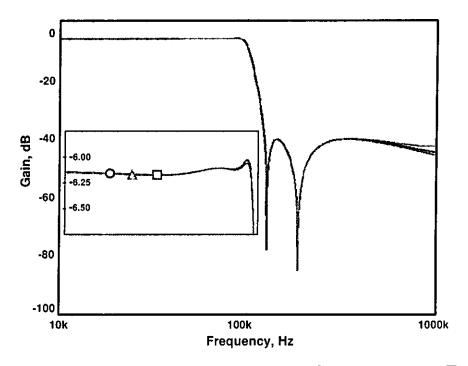

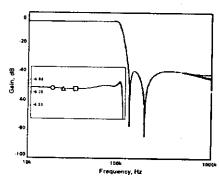

up DC voltage, i.e., such OTA-RC filter requires more power consumption by design. With  $I_N=I_P=2.0\mu A$  (implemented from a simple single-transistor current source), R1=R2=R3=50k $\Omega$  (utilising simple triode NMOS transistors), C1=C2=2pF, the filter ac responses are illustrated in Fig.4.8. At Q~10, the total noise of these three filters (lowpass output) were found to be fairly similar and it was equal to ~ 1×10 $^6$ V $^2$  (integrated noise from 1Hz to 100MHz). The frequency responses of the filter are depicted in Fig.4.8.

(a) Lowpass and bandpass responses

Fig.4.8 Second-order filter ac response

Fig.4.9 THD comparison at  $f_{in} = 100kHz$

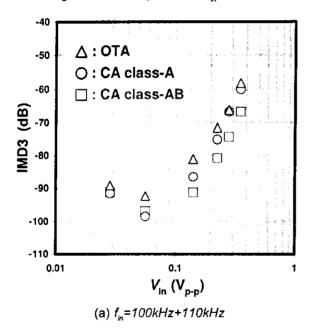

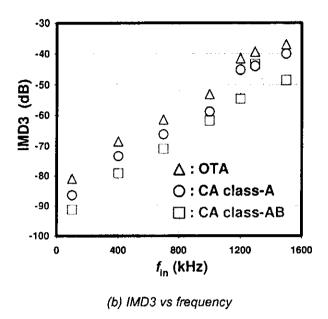

Fig.4.10 IMD3 comparison

Distortion performance comparison of the lowpass output (all with Q~10) is shown in Fig.4.9, Fig.4.10 in which both single-tone and two-tone linearity tests are demonstrated, where THD = total harmonic distortion and IMD3 = third-order intermodulation distortion. Fig.4.10b indicates IMD3 comparison with input frequency sweeps from 100kHz to 1500kHz (for roughly constant output magnitude of -26dBVp for each tone). It can be seen that the proposed current amplifiers render superior performance over the conventional OTA. Improvement over 15dB (for THD) and 10dB (for IMD3) has been noticed. Note that due to the fixed current source I<sub>P</sub>, the lowpass filters implemented with CA in Fig.4.3a and the conventional folded-cascode OTA, i.e., class-A output have the same limited input range of  $2I_P \cdot R = 2 \times 2.0 \mu A \times 50 k\Omega = \pm 0.2 V$ . Moreover, without a negative resistance network connected to the intermediate low impedance node of the folded-cascode OTA, high-Q cannot be attained and linearity is severely degraded because the transconductance of the OTA is not sufficiently high.

#### 4.6 Conclusion

High-gain current amplifiers have been successfully employed as an alternative active building block to conventional operational amplifiers or operational transconductance amplifier in MOSFET-C and active-RC filters. The second-order filters employing the proposed current amplifiers render better linearity performance over the conventional folded-cascode OTA. Future works include utilisation of the proposed amplifiers in high-order filters similar to those in [4.4], [4.5] for practical applications.

<u>:</u>

#### REFERENCES

- [4.1] M. Banu and Y. Tsividis, "The MOSFET-C technique: designing power efficient, high frequency filter," in Design of high frequency integrated analogue filters, edited by Y. Sun, IEE, UK, 2002.

- [4.2] Y. P. Tsividis, "Integrated Continuous-Time Filter Design ——An Overview," *IEEE Journal of Solid-State Circuits*, Vol. 29, No. 3, 1994.

- [4.3] M. Banu and Y. P. Tsividis, "Fully Integrated Active RC Filters in MOS Technology," IEEE Journal of Solid-State Circuits, Vol. SC-18, No. 6, December 1983.

- [4.4] M. Banu and Y. P. Tsividis, "An Elliptic Continuous-Time CMOS Filter with On-Chip Automatic Tuning," *IEEE Journal of Solid-State Circuits*, Vol. SC-20, No. 6, December 1985.

- [4.5] Y. Tsividis, M. Banu and J. Khoury, "Continuous-Time MOSFET-C Filters in VLSI," *IEEE Journal of Solid-State Circuits*, Vol. SC-21, No. 1, February 1986.

- [4.6] E. Sánchez-Sinencio and J. Silva-Martínez, "CMOS transconductance amplifiers, architectures and active filters: a tutorial," IEE Proceedings Circuits, Devices and Systems, Vol. 47, No.1, February 2000.

- [4.7] L. Yao, M. S. J. Steyaert and W. Sansen, "A 1-V 140-□W 88-dB Audio Sigma-Delta Modulator in 90-nm CMOS," *IEEE Journal of Solid-State Circuits*, Vol. 39, No. 11, November 2004.

- [4.8] S. Lindfors, K. Halonen, and M. Ismail, "A 2.7-V Elliptical MOSFET-Only  $g_mC$ -OTA Filter," IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing, Vol. 47, No. 2, February 2000.

- [4.9] C.-C. Hsu and J.-T. Wu, "A Highly Linear 125-MHz CMOS Switched-Resistor Programmable-Gain Amplifier," *IEEE Journal of Solid-State Circuits*, Vol. 38, No. 10, October 2003.

- [4.10] C. Toumazou and J. Lidgey, "Universal Current-Mode Analogue Ampilfiers," in *Analogue IC design: the current-mode approach*, Eds. C. Toumazou, F. Lidgey and D.G.Haigh, IEE, UK, 1990.

- [4.11] G. Palmisano, G. Palumbo and S. Pennisi, "High-Drive CMOS Current Amplifier," *IEEE Journal of Solid-State Circuits*, Vol. 33, No. 2, February 1998.

- [4.12] T. Sato, S. Takagi and N. Jujii, "High Speed Transconductance-C-Opamp Using Current-Feedback Amplifier," *IEICE Trans. Electron.*, Vol.E88-C, No. 6, June 2005.

- [4.13] A. Baschirotto, F. Rezzi, and R. Castello, "Low-voltage balanced transconductor with high input common-mode rejection," *Electronics Letters*, Vol. 30, No. 20, September 1994.

## COMPACT OPERATIONAL TRANSCONDUCTANCE AMPLIFIERS FOR LOW-VOLTAGE MOSFET-C FILTERS

#### 5.1 Introduction

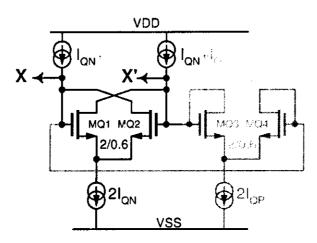

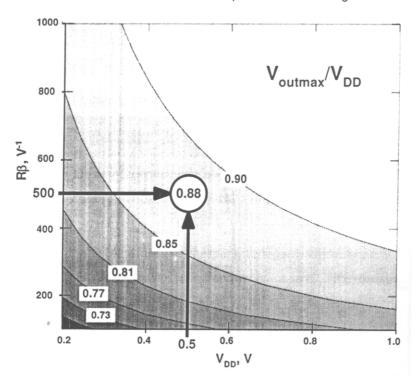

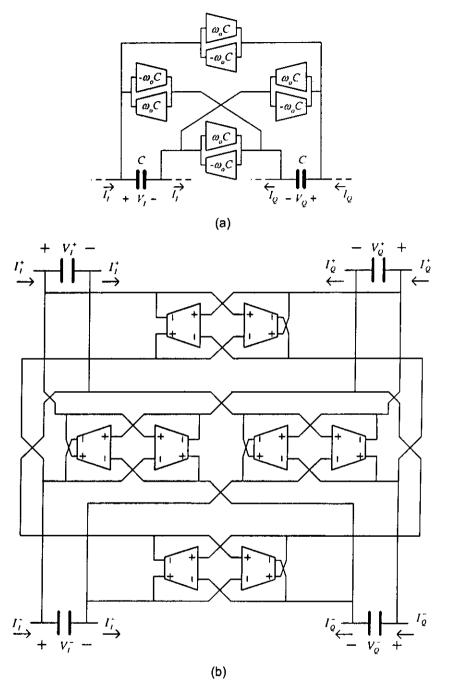

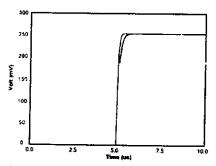

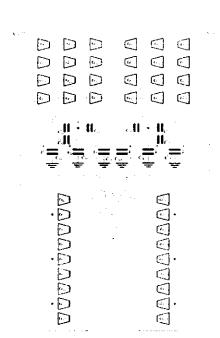

The MOSFET-C filter design technique has portrayed itself as a simple and effective method for integrating high complexity continuous-time filters on a single CMOS chip with large dynamic range and accurate frequency response [5.1]-[5.4]. It has been demonstrated in [5.1] that, instead of using an operational amplifier (OPAMP), an operational transconductance amplifier (OTA) — typically consumes less power than OPAMP — with a sufficiently large transconductance, can be employed as the active building block of the filter. With the push towards low supply voltages in modern fine-line CMOS processes, extensive research efforts have been witnessed on novel low-voltage OTA structures [5.4], [5.5]. This letter introduces a compact two-stage OTA that features a low-voltage class AB output stage with common-mode rejection. The structure and operation of the OTA is described and analysed. This is followed by performance verification via simulation of a 5<sup>th</sup>-order filter operating under a 0.5-V supply voltage.

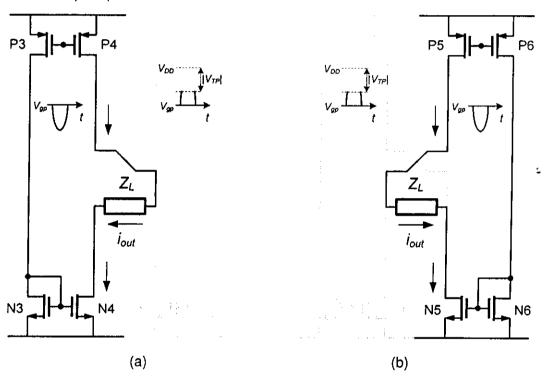

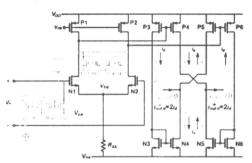

#### 5.2 CIRCUIT DESCRIPTION

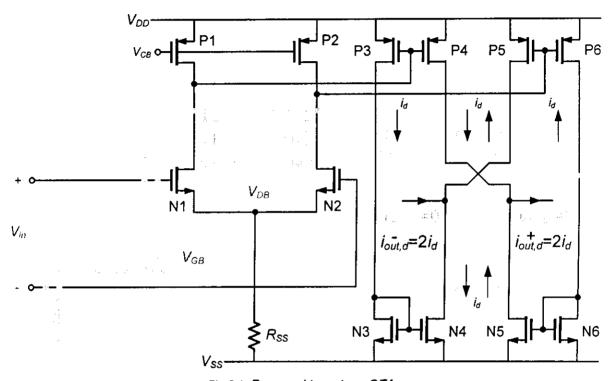

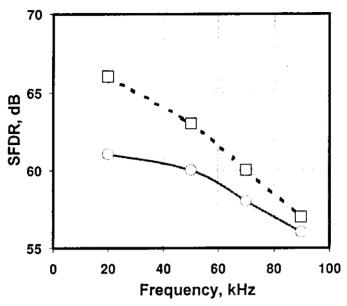

Fig.1 shows the proposed balanced OTA where its input stage utilises a differential amplifier (N1-N2) with a tail bias resistor  $R_{ss}$  and an active load (P1-P2). The use of  $R_{ss}$  reduces the voltage headroom requirement compared to that of a tail current source but at the expense of less common-mode rejection. Each side of the balanced output stages consists of two common-source amplifiers (P3-P4 or P5-P6) and a current-mirror load (N3-M4 or N5-N6) with their outputs crossed connected to those of the opposite balanced stage. Such an arrangement offers simultaneous common-mode signal rejection and class AB operation as will be described shortly. The differential cross-coupling transistors ND1-ND4 and NG1-NG4 with the current source  $I_{BG}$  are included to emulate large biasing

resistors, similar to that employed in the recent low-voltage OTA [5.4], for setting up the DC voltages  $V_D$  and  $V_G$  at the drain and gate terminals of N1-N2. The desired quiescent bias levels are controlled by  $V_{DB}$  and  $V_{GB}$  which are in turn generated by a bias circuitry consisting of two servo loops built around the half-circuit of the OTA. Note that, via a proper sizing, ND1-ND4 can also provide a differential negative resistance for DC gain enhancement [5.4].

Fig.5.1 Proposed two-stage OTA.

The common-mode rejection capability of the output stage can be viewed as a feed-forward operation. This is illustrated by the flow diagram of the common-mode current  $i_{cm}$  in Fig.1 (grey arrows) where  $i_{cm}$  from P3 (P6) is fed forward by the current mirror N3-N4 (N5-N6) to cancel out  $i_{cm}$  from P5 (P4) of the opposite balanced output stage, yielding  $i_{out,cm}^{\dagger} = i_{out,cm}^{\dagger} = 0$ . On the other hand, from the flow diagram of the differential signal  $i_d$  (dark arrows in Fig.1), it can be seen that  $i_d$  adds constructively to produce  $i_{out,d}^{\dagger} = i_{out,d}^{\dagger} = 2i_d$ . Unlike the feed-forward common-mode rejection technique in [5.6], the output stage of Fig.1 also provides a differential current gain factor of two and it thus entails no penalty on the transconductance/bias-current efficiency of the OTA.

To demonstrate the class AB operation, two extreme cases of differential signal excursion are illustrated in Fig.2. On one side of the balanced output stage, the gate voltage,  $V_{gp}$ , is above  $V_{DD}$  –

$|V_{TP}|$  (or the source-gate voltage  $V_{sgp} < |V_{TP}|$ ) driving all the associated transistors into the cut-off region (as visualised in grey in Fig.2) and hence no output current is supplied. On the other side,  $V_{gp}$  is below its quiescent value enabling the transistors on this side to continue supplying the output current to the load  $Z_L$ . In effect, the class AB stage operates in a lateral manner where one side of the balanced output can supply the load current while the other side is off. When compared to the conventional push pull complementary MOS stage, this lateral class AB output has potential for a lower voltage operation since the minimum supply voltage requirement is not limited by the gate-source stacking of the conventional push-pull CMOS transistors.